〈系统与设计〉

## 用于图像传感器的扩展计数模数转换器设计

郭 强, 陈 楠, 姚立斌

(昆明物理研究所, 云南 昆明 650223)

**摘要:** 扩展计数(extended counting)模数转换器(ADC)合并了Sigma-Delta( $\Sigma\Delta$ )ADC的高精度和奈奎斯特率ADC的高速低功耗优势, 具有中高精度和中等的转换速度, 在图像传感器方面具有很好的应用前景。以 $\Sigma\Delta$ ADC与逐次逼近(SAR)ADC的组合结构的扩展计数ADC为例, 基于0.35 μm的CMOS工艺, 对其进行了电路层面的设计。通过电路级仿真验证了该工艺下ADC的功能并且得到了部分的性能参数。

**关键词:** 扩展计数; 模数转换器; 图像传感器; 读出电路

中图分类号: TN492 文献标识码: A 文章编号: 1001-8891(2016)06-0188-05

## Design of Extended Counting ADC Applied in Image Sensors

GUO Qiang, CHEN Nan, YAO Libin

(Kunming Institute of Physics, Kunming 650223, China)

**Abstract:** The extended counting analog-to-digital converter (ADC) combines the accuracy of  $\Sigma\Delta$ ADC and the speed and power consumption of Nyquist-rate ADC. It has a good application foreground for its high resolution with a medium conversion speed. The combination of  $\Sigma\Delta$ ADC and successive approximation register (SAR) ADC has been chosen as the structure of extended counting ADC, and the extended counting ADC has been designed and simulated based on the 0.35 μm CMOS technology. The extended counting ADC has been verified and some properties have been given by the simulation.

**Key words:** extended counting, analog-to-digital converter, image sensor, readout circuit

### 0 引言

随着电子技术水平的提高, 图像传感器也向着数字化的方向不断发展。与传统的模拟电路相比, 数字化后的图像传感器具有更好的抗干扰性能, 并降低整个成像系统的成本和复杂度<sup>[1]</sup>。图像传感器的数字化需要额外的模数转换器(ADC)电路, 因此也不可避免地带来了电路功耗的上升。同时, 数字化后整个图像传感器的输出由ADC转换为数字信号, 其性能受限于该ADC的精度和转换速度。因此, 用于图像传感器的ADC电路具有速度、精度功耗方面的要求, 同时鉴于不同的应用方式还有尺寸方面的限制。

$\Sigma\Delta$ ADC具有很高的精度, 其通过对信号的过采样来降低噪声的影响, 以此提高转换的精度<sup>[2]</sup>, 也叫

过采样ADC。但是过采样的转换过程增加了处理的数据量, 降低了转换速度并增加了功耗, 限制了其在图像传感器中的应用。相对于 $\Sigma\Delta$ ADC, SAR ADC为代表的奈奎斯特率ADC, 由于其对信号以奈奎斯特率进行采样和转换, 转换过程处理的数据量大大降低, 因此速度远胜 $\Sigma\Delta$ ADC, 功耗也更低, 但是很难取得较高的精度。为了缩小上述ADC的不足, 平衡它们在速度、功耗和精度等方面的性能, 便产生了扩展计数ADC这种结构。

扩展计数ADC融合了 $\Sigma\Delta$ ADC和奈奎斯特率ADC的结构, 并将每一次转换过程分成了2个阶段<sup>[3-7]</sup>, 分别交由 $\Sigma\Delta$ ADC和奈奎斯特率ADC进行处理, 并以此在 $\Sigma\Delta$ ADC的精度和奈奎斯特率ADC的速度、功耗方面取得了平衡<sup>[3,4,6-8]</sup>。同时, 扩展计数ADC又有

收稿日期: 2015-12-10; 修订日期: 2016-03-04。

作者简介: 郭强(1987-), 男, 陕西咸阳人, 硕士研究生, 研究方向为混合信号集成电路设计。

基金项目: 云南省科技厅应用基础研究计划重大项目(2013FC009)。

着较为简单的结构, 能够更好地应用于图像传感器读出电路。

## 1 原理

扩展计数转换这种技术, 将每一次转换分解成粗、细两个转换过程。先对输入的模拟信号进行计数转换, 实现粗转换。待粗转换完成后, 再对余下的部分进行细分, 完成扩展转换以实现细转换<sup>[3,6,9]</sup>。转换完成后, 输入可表示为:

$$V_{\text{IN}} = a \times U_1 + b \times U_2 \quad (1)$$

式中:  $V_{\text{IN}}$  是输入的模拟信号;  $a$ 、 $b$  分别是粗、细转换的转换结果;  $U_1$ 、 $U_2$  分别是粗、细转换的单位。

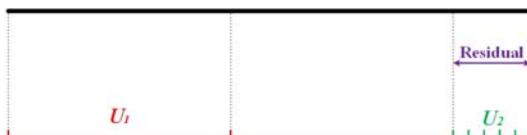

扩展计数转换的原理如图 1 所示, 其转换过程相当于用不同刻度的尺子对物体进行测量。先用以  $U_1$  为单位的尺子, 完成宏观尺度上的预估; 对于超出, 却又不足  $U_1$  的部分, 可用  $U_2$  尺度的尺子进行精确的测量。

图 1 扩展计数转换原理

Fig.1 Principle of the extended counting

用于计数转换的 ADC, 通常选择一阶  $\Sigma\Delta$  ADC。因为  $\Sigma\Delta$  ADC 可以通过对输入信号的过采样, 来降低噪声的影响, 以提高整个 ADC 的精度。为了提高整个转换的速度, 用于扩展转换的 ADC, 一般则选择一些如 SAR ADC、单斜率 (single slope) ADC<sup>[10]</sup>、循环 (cyclic) ADC<sup>[11]</sup> 等奈奎斯特率 ADC<sup>[7]</sup>。

## 2 电路拓扑结构

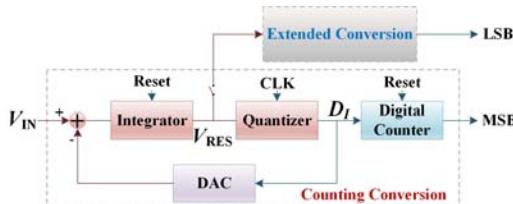

设计的扩展计数 ADC 由 1 个一阶  $\Sigma\Delta$  ADC 和 SAR ADC 组合而成。用于实现扩展计数转换的 ADC 的基本结构如图 2 所示。

图 2 扩展计数 ADC 拓扑结构

Fig.2 Block diagram of the extended counting

输入信号通过  $\Sigma\Delta$  ADC, 完成了计数转换, 可以得到一组数字输出  $D_I$  和积分器上剩余电压的  $V_{\text{RES}}$  (余量电压)。接着  $D_I$  会由数字累加器统计得到扩展计数

ADC 输出的高有效位 (MSB)<sup>[3-8]</sup>; 而  $V_{\text{RES}}$  则被送入奈奎斯特率 ADC 接受扩展转换, 并得到扩展计数 ADC 的低有效位 (LSB)。上述转换过程可以分别表示为:

$$V_{\text{IN}} = 2^{-M_1} \times \left( \sum_{I=1}^{2^{M_1}} D_I \times V_{\text{REF}_1} + \frac{C_1}{C_s} \times V_{\text{RES}} \right) \quad (2)$$

$$V_{\text{RES}} = \sum_{J=1}^{M_2} 2^{-J} B_J V_{\text{REF}_2} + \varepsilon \quad (3)$$

式中:  $V_{\text{IN}}$  是 ADC 的输入信号;  $M_1$  和  $M_2$  分别是  $\Sigma\Delta$  ADC 和奈奎斯特率 ADC 的精度;  $V_{\text{REF}_1}$  和  $V_{\text{REF}_2}$  分别是  $\Sigma\Delta$  ADC 和奈奎斯特率 ADC 的基准电压;  $C_1$  和  $C_s$  分别是  $\Sigma\Delta$  ADC 中积分器的积分电容和采样电容;  $B_J$  和  $\varepsilon$  分别是奈奎斯特率 ADC 的数字输出和转换误差。合并(2)、(3)式, 可以得到整个扩展计数过程的转换结果:

$$V_{\text{IN}} = \frac{\left( \sum_{I=1}^{2^{M_1}} D_I V_{\text{REF}_1} + \frac{C_1}{C_s} \sum_{J=1}^{M_2} 2^{-J} B_J V_{\text{REF}_2} \right)}{2^{M_1}} + \frac{C_1}{C_s} \times \frac{\varepsilon}{2^{M_1}} \quad (4)$$

通过式(4), 可以看出扩展计数 ADC 的输入最终被转换成  $D_I$  和  $B_J$  两部分数字信号与转换误差  $\varepsilon$  的和。通过扩展计数转换, ADC 的转换误差被减小到  $C_1/(C_s \times 2^{M_1})$  倍, 转换精度得以提高<sup>[6]</sup>。

整个扩展计数转换的精度是  $M_1+M_2$  位, 需要耗费  $2^{M_1}+M_2$  个时钟周期, 与之相比, 精度为  $M_1+M_2$  位的  $\Sigma\Delta$  ADC 一次转换需要  $2^{M_1+M_2}$  个时钟周期, 可见其转换速度大大提高。

## 3 电路实现

为了适应图像传感器应用的需要, 通常需要 ADC 要达到 14 位的精度且要求其尽可能小的功耗和面积, 同时要求 ADC 至少要达到 30 kS/s 的转换速度。

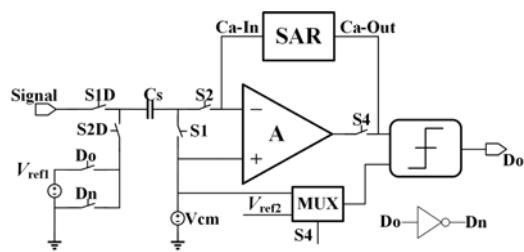

基于功耗等方面的原因, 选择了一阶增量型  $\Sigma\Delta$  和 SAR ADC 的组合形式作为扩展计数 ADC 的基本结构, 其电路构成如图 3 所示。

图 3 扩展计数 ADC 的电路结构

Fig.3 Structure of extended counting ADC

图3中,扩展计数ADC使用了loading-free技术(使用SAR电容阵列替代 $\Sigma\Delta$ ADC中的积分电容参与计数转换)<sup>[5,9]</sup>。使用该技术后电路具有以下优点:①节省电路面积。loading-free技术引入后,电路节省了一个积分电容。通常电容在芯片中会占用大量面积,因此该技术对于提高芯片利用率有重大意义。②使用loading-free技术后,计数转换后的余量电压直接保存在SAR ADC的电容阵列上,节省了二次转换的采样周期,同时也避免了二次采样过程中余量电压的损耗,在一定程度上提高了ADC的精度。

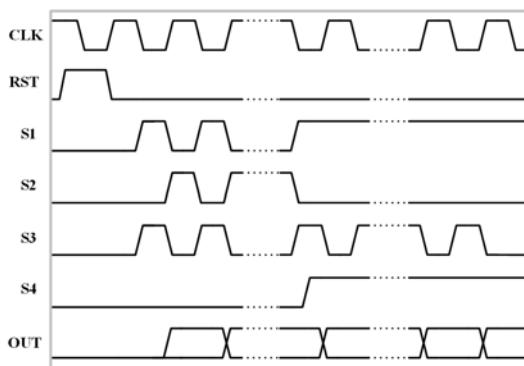

用于控制扩展计数ADC工作的时钟序列如图4所示。

图4 扩展计数ADC的控制时序

Fig.4 Timing diagram for the extended counting ADC

其中CLK是电路主时钟;RST是全局电路复位信号,用于每次转换开始时对电路各模块进行初始化,同CLK一样由外部电路提供;S1、S2是对积分器的控制信号;S3是动态比较器的控制信号;S4是电路工作模式的控制信号,其高电平时ADC工作在计数转换状态,低电平时工作在扩展转换状态。

在确定了上述结构的基础上,综合多种因素选择了6位 $\Sigma\Delta$ ADC和8位SAR ADC的组合,进行设计。基于以上组合,可知扩展计数ADC的转换周期需要至少 $72(2^6+8=72)$ 个时钟。因此,为了实现不低于30kS/s的转换速度,需要保证ADC电路时钟驱动的频率不低于2.16MHz( $72\times30\text{kHz}$ )。本文中的ADC选择了3MHz的时钟频率,可以实现40kS/s的转换速度。

确定了以上性能参数后,通过行为级仿真,就可以得到各模块的具体性能要求,并基于仿真结果,进行电路子模块的设计。

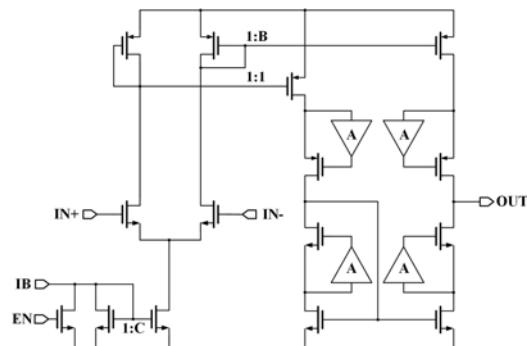

### 3.1 运算放大器

通过对ADC的行为级仿真,可以得到6位 $\Sigma\Delta$ ADC和8位SAR结构的扩展计数ADC为了获得足够的精度,要求运算放大器的性能需要达到80dB增益和10倍电路工作频率的带宽要求。结合电路工作稳定性的需要,最终可以得到运放的性能指标为80

dB增益,30MHz带宽和不低于60°的相位裕度。

针对以上的性能要求,运放的设计采用了共源共栅(cascode)结构的电流镜运放,其在0.35μm CMOS工艺下可实现60dB的增益,不足的20dB增益可以通过4个辅助运放单元,采用增益自举(gain booster)的结构来弥补<sup>[12-15]</sup>,具体的电路结构如图5所示。

图5 带增益自举结构的运算放大器

Fig.5 Structure of the amplifier with gain booster

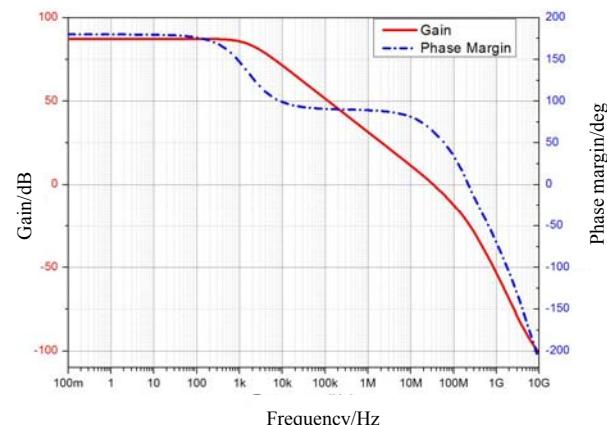

图中EN(低有效)作为运放的工作开关,其作用是可以在ADC运行在扩展转换阶段关闭运算放大器,以节省功耗。为了适应图像传感器应用的需要,设计的运放采用了差分输入,单端输出的结构,其仿真结果如图6所示。

图6 运算放大器仿真结果

Fig.6 Property of the amplifier by simulation

可以看出,该运放是一个多极点系统,其主极点位于1kHz处,第2个极点在60MHz附近。整个运放的性能达到了88dB的增益和32MHz的带宽,相位裕度约65°,同时可以测得其功耗约为65μW,可以满足扩展计数ADC在图像传感器中应用的需要。

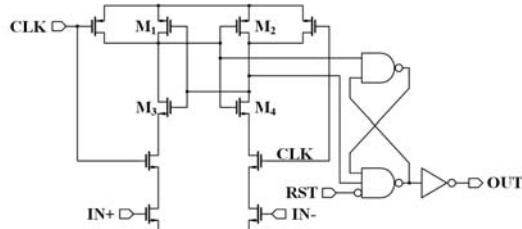

### 3.2 比较器

图7所示为该扩展计数ADC中使用的比较器结构。该动态比较器由时钟信号CLK的低电平控制,定期向PMOS管M<sub>1</sub>~M<sub>4</sub>的栅极充电,并在CLK的高电平时对其放电。因为在放电过程中,输入NMOS

对管的栅电压不同,使其放电电流也不同,放电时间就存在差异。于是,先放电完成的支路会拉低另一个支路的PMOS管栅电压并拉高输出,同时本支路的PMOS栅电压被拉高和输出被拉低,以此得到比较结果,维持比较结果并输出,之后等待下一个时钟周期的到来。

该结构的优点在于静态功耗几乎为0,只在时钟信号发生变化时消耗少量功耗。对于其性能指标,要求比较器能够在ADC的工作频率下正常工作,且分辨率小于ADC的 $0.5 \times \text{LSB}$ <sup>[2]</sup>。

图7 动态比较器结构

Fig.7 Structure of the dynamic comparator

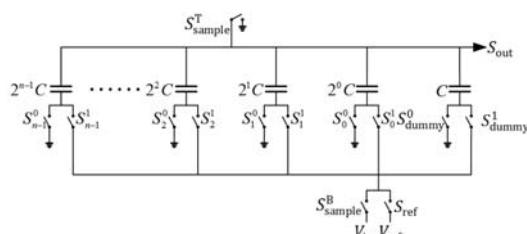

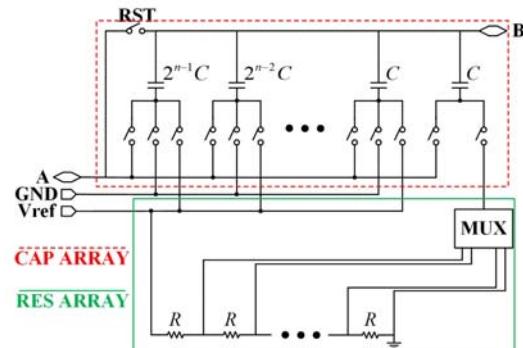

### 3.3 SAR DAC 电容阵列

传统的SAR DAC电容阵列是由 $M_2+1$ 个( $M_2$ 是SAR ADC的精度)电容并联组成的,并通过开关控制,其具体的结构如图8所示。

图8 SAR DAC 电容阵列结构

Fig.8 Structure of the SAR DAC

可以看到,该SAR DAC总的电容大小为 $2^{M_2} \times C$ ,所需的电容大小随精度以指数形式增加<sup>[2]</sup>。因此对于精度较高的SAR ADC,其电容阵列会占用大量的电路面积。为了减小在SAR电容阵列方面的电路面积消耗,本设计中的SAR DAC阵列选择了C-R结构的DAC阵列<sup>[16]</sup>,其结构如图9所示。

在图9中,一个 $M_2$ 位的SAR DAC由 $n$ 个电容阵列和 $2^m$ 个电阻阵列( $n+m=M_2$ )组合构成。SAR DAC的电容阵列面积却缩小为原来的 $1/2^m$ 。由于电阻阵列可由多个ADC单元公用,因此电阻阵列的功耗和面积几乎可以忽略。这在图像传感器中的应用是十分有利的。

### 3.4 相关的数字电路

扩展计数ADC中使用到的数字电路主要有时钟产生电路、数字累加器和SAR DAC的逻辑控制单元。

图9 C-R结构的SAR DAC

Fig.9 C-R Structure of the SAR DAC

其中,时钟产生电路用于产生各模块所需的时钟信号,完成对整个电路总的控制功能;由于整个ADC仍是基于开关电容阵列工作的,所以要求其产生非交叠的时钟。数字累加器则用于对计数转换中产生的比较器结果进行统计,产生并保存整个扩展计数转换的MSB。SAR DAC逻辑控制单元,在时钟产生单元的控制下实现对SAR DAC电容阵列参与转换的行为控制,并保存扩展转换的结果。其具体的结构都比较成熟,这里不再过多叙述。

## 4 仿真结果

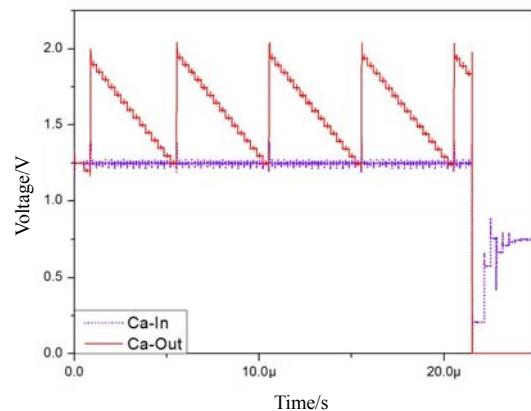

本节的测试结果是在 $0.35\mu\text{m}$ 的CMOS工艺下设计,并通过Spectre仿真器进行仿真。图10是该ADC在瞬态仿真中积分器的输入输出波形。可以明显的看出扩展计数转换的两步转换过程。在计数转换阶段,信号通过SAR电容阵列的输入端Ca-In,对积分电容进行充电,并将积分结果通过其输出端Ca-Out送至比较器。在扩展转换阶段,电容阵列的输入输出对调,每一步的转换结果由其输入端Ca-In输出到比较器进行比较。

图10 积分器输入输出曲线

Fig.10 Input and output of the integrator

同时,我们还可以更直观地看到两步转换的速度差别。计数转换占用了64个时钟周期来完成14位扩

展计数转换中的高 6 位,需要花费整个转换周期的 80%以上;而扩展转换则只花费不到 20%的转换周期,就完成了余下的 8 位数据的转换。通常,在转换速度和功耗都允许的情况下,应该尽量选择更高精度的计数转换,以提高整个 ADC 的有效精度。同时,通过图 10 还可以看到,在扩展转换阶段由于运算放大器停止了工作,所以 Ca-Out 端的电压降低到了 0 电位。

通过对扩展计数 ADC 的瞬态仿真,可测得其平均功耗为  $93.6 \mu\text{W}$ ,其中模拟部分  $61 \mu\text{W}$ ,数字部分  $32.6 \mu\text{W}$ 。

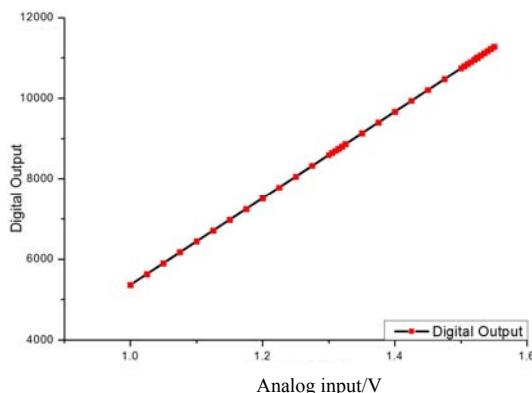

扩展计数 ADC 的输入输出曲线仿真如图 11 所示。该 ADC 显示了良好的线性度。

图 11 扩展计数 ADC 输入-输出特性曲线仿真结果

Fig.11 Input-output characteristic curve by simulation

## 5 结论

从电路的角度分析了扩展计数 ADC 的原理和结构,并设计了一款扩展计数结构的 ADC。该 ADC 基于  $0.35 \mu\text{m}$  的 CMOS 工艺进行设计,结合了 6 位的  $\Sigma\Delta$ ADC 和 8 位的 SAR ADC,能够达到  $40 \text{kS/s}$  的转换速度。设计中使用了 loading-free 技术的扩展计数 ADC 结构和 C-R 型的 SAR DAC 结构,减小了电路面积的同时提高了电路的精度。通过仿真得到了其正常工作时的功耗为  $93.6 \mu\text{W}$ ,并验证了其良好的线性度,验证了其用于图像传感器电路中的可行性。

## 参考文献:

- [1] 姚立斌. 低照度 CMOS 图像传感器技术[J]. 红外技术, 2013, 35(3): 125-132.

YAO Li-bin. Low-light-level CMOS image sensor technique[J]. *Infrared Technology*, 2013, 35(3): 125-132.

- [2] Franco Maloberti. *Data Converter*[M]. Berlin: Springer-Verlag, 2007.

- [3] Pieter Rombouts, Wim De Wilde, Ludo Weyten. A 13.5-b 1.2-V micropower extended counting A/D converter[J]. *IEEE Solid-State Circuits*, 2001, 36(2): 176-183.

- [4] Jeroen De Maeyer, Pieter Rombouts, Ludo Weyten. A double-sampling extended-counting ADC[J]. *IEEE Solid-State Circuits*, 2004, 39(3): 411-418.

- [5] Chao I Jen, Huang Chiachun, Wu Yingcheng, et al. A 12-bit 4-kHz incremental ADC with loading-free extended counting technique[C]//2<sup>nd</sup> International Symposium on Next Generation Electronics, 2013: 29-32.

- [6] CHEN Honglei, WU Dong, SHEN Yanzhao, et al. A low power 14 bit 51.2 kS/s double-sampling extended counting ADC with a class-AB OTA[J]. *Journal of Semiconductors*, 2012, 33(9): 095004.

- [7] 陈楠, 姚立斌. 阵列型图像传感器模数转换技术[J]. 红外技术, 2014, 36(10): 769-776.

CHEN Nan, YAO Libin. Analog to digital conversion techniques in array image sensors[J]. *Infrared Technology*, 2014, 36(10): 769-776.

- [8] Woo D H, Kim C B, Lee H C. Current input extended counting ADC with wide dynamic range for LWIR FPAs[J]. *IEEE Sensors Journal*, 2009, 9(4): 441-448.

- [9] Jansson C. A high-resolution, compact, and low-power ADC suitable for array implementation in standard CMOS[J]. *IEEE Transactions on Circuits Syst. I*, 1995, 42(11): 901-912.

- [10] Chen C H, Jung Y, Ceballos J L, et al. Multi-step extended counting analog-to-digital converters[J]. *Electronics Letters*, 2013, 49: 30-31.

- [11] Kim J H, Jung W K, Lim S H, et al. A 14b extended counting ADC implemented in a 24 Mpixel APS-C CMOS image sensor[C]// *International Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, IEEE, 2012: 390-39.

- [12] Willy M C Sansen. *Analog Design Essentials*[M]. Berlin: Springer-Verlag, 2006.

- [13] Behzad Razavi. *Design of Analog CMOS Integrated Circuits*[M]. New York: McGraw-Hill Education, 2000.

- [14] 何乐年, 王忆. 模拟集成电路设计与仿真[M]. 北京: 科学出版社, 2008.

HE Lenian, WANG Yi. *Design and Simulation of Analog Integrated Circuits*[M]. Beijing: Science Press, 2008.

- [15] Paul R Gray, Paul J Hurst, Stephen H Lewis, et al. *Analysis and Design of Analog Integrated Circuits* [M]. New York: John Wiley & Sons, 2001.

- [16] Chen Shan, Tong Xingyuan, Cai Naiqiong, et al. A 12-bit 1 MS/s Non-calibrating SAR A/D converter based on 90 nm CMOS process[C]//MVHI, 2010.