# 大面阵红外图像高速传输系统设计

张承泓, 李范鸣

(中国科学院上海技术物理研究所, 上海 200083)

**摘要:** 探讨了一种大面阵红外图像高速传输系统的原理、结构及其实现。针对红外成像系统的要求, 提出了一种基于 FPGA 的大面阵红外图像高速传输方法, 并利用光纤传输技术与 aurora 协议来实现。该方案不仅实现了大面阵红外图像的高速传输, 而且实现了高速、可靠的指令通信。

**关键词:** 大面阵红外图像; 高速传输; aurora 协议; 光纤传输; UFC

中图分类号: TN216 文献标识码: A 文章编号: 1001-8891(2014)12-0958-03

## High-speed Transmission System of Large-Array IR Image

ZHANG Cheng-hong, LI Fang-ming

(Shanghai Institute of Technical Physics of the Chinese Academy of Sciences, Shanghai 200083, China)

**Abstract:** The principle, architecture and implementation technologies of large-array infrared image high-speed transmission system have been discussed. Aiming at the application requirement of infrared imaging system, a new method for large-array infrared image high-speed transmission has been proposed based on FPGA, which is realized by using Aurora 8B/10B protocol and optical fiber transmission technology. The scheme has realized both high-speed transmission of large-array infrared image and efficient communication of instructions which is less susceptible to interference.

**Key words:** large-array IR image, high-speed transmission, Aurora 8B/10B protocols, fiber, UFC

## 0 引言

红外成像技术在众多领域都占有相当重要的位置, 它具有很强的抗干扰能力, 可以穿透浓烟, 浓雾, 黑夜, 伪装等识别一定的目标, 而且可以提供 24 h 全天时的服务。随着人们对红外成像系统空间分辨率要求的提高, 凝视型红外探测器向大面阵方向发展, 数据的容量越来越大, 使得系统对图像传输和处理的实时性要求越来越高。此外, 目前红外成像系统中通常使用串口进行指令通信, 而串口存在传输速度慢、易受干扰等缺点。

针对上述问题, 本文将光纤传输技术与 aurora 协议相结合, 设计了一个大面阵红外图像高速传输系统, 并充分利用 Xilinx 公司提供的 aurora IP 核, 简化 FPGA 逻辑设计。该系统已应用到实际红外成像系统中, 取得了较好的效果。

## 1 大面阵红外图像高速传输系统

### 1.1 系统架构

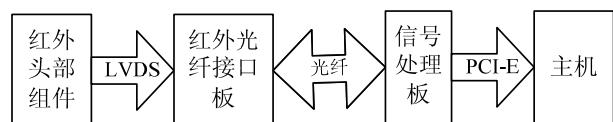

大面阵红外图像高速传输系统的系统框图如图 1

所示。

整个系统数据流如下: 红外头部组件输出数字图像至红外光纤接口板, 红外光纤接口板将数字图像叠加系统相关信息(方位、俯仰、系统状态信息等)后通过高速光纤发送至红外信号处理板<sup>[1]</sup>, 信号处理板通过 PCI-E 协议将图像传送至主机<sup>[2-3]</sup>。信号处理板与光纤接口板之间的指令交互通过高速光纤来完成。

图 1 系统架构 Fig.1 System Structure

光纤接口板与信号处理板都选用 Xilinx 公司的 Viretx-5 系列的 FPGA 作为核心控制器件。该系列 FPGA 内置 PCI-E 集成端点模块<sup>[4]</sup>和 RocketIO GTP<sup>[5]</sup>, 利用 aurora IP 核<sup>[6]</sup>可实现光纤接口板与信号处理板的光纤传输; 使用 Endpoint Plus for PCI Express IP 核<sup>[7]</sup>可实现符合 PCI-E 总线协议的数据传输。

### 1.2 红外图像高速传输机制

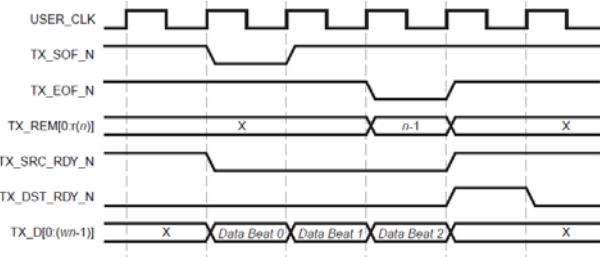

本系统在实际设计中利用了 Xilinx 公司提供的

Aurora IP 核，线速（Line Rate）设为 1.25 Gbps，数据位宽设为 16 bit，工作模式设为 Full-Duplex Framing 模式。实际传输过程中，将一帧图像分成 512 行，每行 640 个 Word，一行即为 Aurora 8B/10B 协议中的一帧。在第 512 行后，新一帧图像传输前加入第 513 行，该行大小同样为 640 个 Word。该行信息为整个系统的辅助状态信息。由于每发送一定的 Bytes，需要发送一次时钟相位补偿序列，固在行与行之间的空闲态发送时间补偿序列，以调整光纤发送端与接收端的时钟相位偏差。如不进行适当的时钟补偿，数据传输将出现较高的误码率。Framing 模式的发送时序如图 2 所示。TX\_SOF\_N 有效表示一帧传输开始，TX\_EOF\_N 有效表示一帧传输结束，TX\_SRC\_RDY\_N 有效表示传输数据有效，TX\_DST\_RDY\_N 有效表示可发送数据。

图 2 光纤发送时序 Fig.2 Data Transfer

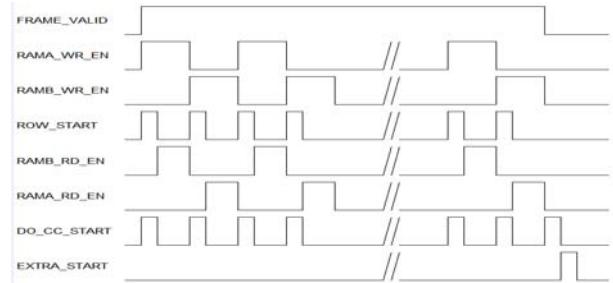

具体的红外图像传输机制如图 3 所示。FRAME\_VALID 为图像帧有效信号；ROW\_START 为图像行起始信号；EXTRA\_START 为辅助信息行起始信号；RAMA\_WR\_EN、RAMB\_WR\_EN 分别为 RAM\_A、RAM\_B 写使能信号；RAMA\_RD\_EN、RAMB\_RD\_EN 分别为 RAM\_A、RAM\_B 读使能信号；DO\_CC\_START 为时钟补偿序列起始信号。当 FRAME\_VALID 有效时，顺序写入一行图像数据至 RAM\_A，并置 ROW\_START 有效，接着顺序写入一行图像数据至 RAM\_B，并置 ROW\_START 有效，接着顺序写入一行图像数据至 RAM\_A，并置 ROW\_START 有效，如此反复，直至 FRAME\_VALID 无效，并置 EXTRA\_START 有效。当 ROW\_START 有效后，进行时钟补偿，而后从 RAM\_B 中读出数据用光纤发送至主机；当下一个 ROW\_START 有效后，进行时钟补偿，而后从 RAM\_A 中读出数据用光纤发送至主机；如此反复，直至发送完 512 行图像数据。当 EXTRA\_START 有效后，发送一帧辅助信息行至主机。

### 1.3 系统指令通信传输机制

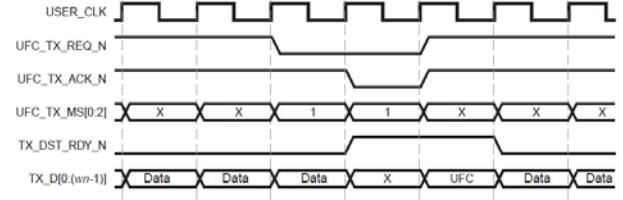

由于光纤接口板与信号处理板之间只有一个光纤通道，系统的图像传输与指令传输都是通过该通道来完成的，如何协调图像传输与指令传输是个关键的

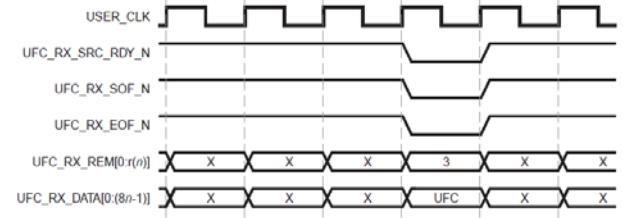

问题，本文设计了一个简单有效的传输机制来解决该问题。aurora IP 核的 UFC 模块是在 Framing 模式下可选的一种流控制模式，该模块可在正常传输的数据流中添加控制信息，十分适合用于系统指令传输。UFC 模式下的发送与接收时序如图 4、图 5 所示。UFC\_TX\_REQ\_N 有效表示向核请求发送 UFC 数据，UFC\_TX\_ACK\_N 有效表示核应答了该发送请求，在该应答后的下一个时钟开始，可发送 UFC 数据。UFC\_RX\_SRC\_RDY\_N 有效表示接收的 UFC 数据有效，UFC\_RX\_SOF\_N 有效表示一帧 UFC 帧的帧起始，UFC\_RX\_EOF\_N 有效表示一帧 UFC 帧的帧结束。

图 3 红外图像传输机制

Fig.3 The transmission mechanism of infra-red image

图 4 单周期 UFC 发送时序

Fig.4 Transmitting a single-cycle UFC message

图 5 单周期 UFC 接收时序

Fig.5 Receiving a single-cycle UFC message

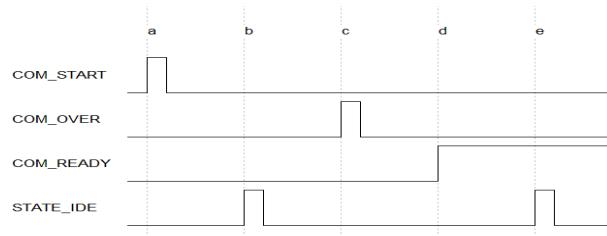

具体的指令通信传输机制如图 6 所示。COM\_START 为指令帧起始信号；COM\_OVER 为指令帧结束信号；COM\_READY 为指令帧准备好信号；STATE\_IDE 为图像传输状态空闲信号。当 COM\_START 有效，系统将指令帧数据顺序写入 FIFO 中，直至 COM\_OVER 有效。在 COM\_OVER 有效后从 FIFO 中读出该指令帧并处理该指令，将需要返回的指令数据写入 FIFO 中，同时置 COM\_READY 有效。每当 STATE\_IDE 有效时，查询 COM\_READY 是否有效，有效时从 FIFO 中读出指令数据并启动一个 UFC 发送。在 b

时刻,由于 COM\_READY 无效,该指令帧将在 e 时刻发送。

图 6 指令通信传输机制

Fig.6 The transmission mechanism of command

## 2 实验结果

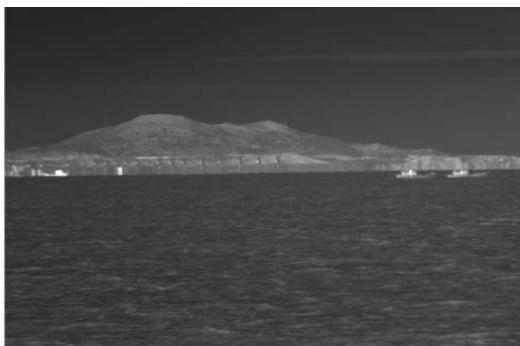

本文设计的系统实际应用在一个红外跟踪系统中,该系统传输的一帧图像的大小为  $640 \times 513$  个 word, 图像帧频为 100 帧/s。一帧图像的数据容量为  $640 \times 513 \times 2 = 656640$  Byte = 0.64125 MByte, 数据率为  $0.64125$  MByte/ $0.01$  s = 64.125 MByte/s。图 7 为系统采集到的红外图像。从图中可以看出,纹理清晰,轮廓分明,效果良好。为了测试本系统传输的极限数据率,提高红外图像的帧频,当图像帧频为 200 帧/s 时,系统仍能正常稳定工作。当图像帧频大于 200 帧/s,会出现丢帧现象。故该系统数据传输的极限数据率为 131.2 MByte/s。

图 7 大面阵红外图像

Fig.7 Large-array infrared image

为了测试改进的指令通信系统性能,设计了以下实验。实验 1 中主机通过串口发送 1000 个指令包(16 个 Byte)至光纤接口板,检验光纤接口板能收到的正确指令包的个数。串口波特率分别设为 115200, 230400, 指令包以 100 帧/s, 200 帧/s 的间隔连续发送, 表 1 为实验结果。实验 2 中主机通过本系统以不同的间隔发送 1000 个指令包, 表 2 为实验结果。从表中可以看出,串口在高波特率、高帧频的情况下容易产生误码。而本系统的指令通信能达到 1000 帧/s 的传输速度,且无误码。

表 1 指令通信实验 1

Table 1 Communication test one

|        | 发送方式       |            |            |            |

|--------|------------|------------|------------|------------|

|        | 115.2k/100 | 230.4k/100 | 115.2k/200 | 230.4k/200 |

| 发送的指令包 | 1000       | 1000       | 1000       | 1000       |

| 接收的指令包 | 995        | 990        | 993        | 988        |

表 2 指令通信实验 2

Table 2 Communication test two

| 发送方式   | 100 帧/s | 500 帧/s | 800 帧/s | 1000 帧/s |

|--------|---------|---------|---------|----------|

| 发送的指令包 | 1000    | 1000    | 1000    | 1000     |

| 接收的指令包 | 1000    | 1000    | 1000    | 1000     |

## 3 结论

目前红外图像传输系统大多采用以下两种方案:一是 LVDS 传输,二是 USB 传输。LVDS 标准推荐的最高数据传输速率是 655 Mbps, 即 81.875 MByte/s。其有以下缺点:一是需要多对差分线同时传输,才能达到较高的数据传输率,对系统的布线有严苛的要求,多对信号之间容易不同步;二是数据高速传输时容易受到外界干扰导致数据出错。常用的 USB2.0 传输的最高传输速率是 480 Mbps, 即 60 MByte/s, 数据传输速率与本系统相比有明显差距,且 USB 传输的距离有限。故本文设计的系统在高数据率、传输距离远、外界干扰较强的系统中有显著优势。此外,利用光纤替代串口进行指令通信,提高了系统的可靠性,加快了指令通信的传输速度。

## 参考文献:

- [1] 黄新栋,赵佳.大视场线扫红外图像的高速传输系统[J].红外技术,2010,32(1): 37-40.

- [2] 兰春嘉,汤心溢,王世勇,等.基于 SOPC 的红外图像采集系统[J].红外技术,2011,33(1): 37-40.

- [3] 王宇,汤心溢,刘鹏,等.拼接型长线列红外双波段图像实时传输系统[J].红外技术,2013,35(2): 69-73.

- [4] Xilinx Inc. Virtex-5 FPGA integrated endpoint block for PCI express designs[EB/OL]. 2008[2012-04-05]. <http://www.xilinx.com/support/>.

- [5] Xilinx Inc. Virtex-5 FPGA RocketIO GTP Transceivers [EB/OL]. 2009 [2012-04-05]. <http://www.xilinx.com/support/>.

- [6] Xilinx Inc. LogiCORE IP Aurora 8B/10B v5.1 [EB/OL]. 2009[2011-09-24]. <http://www.xilinx.com/support/>.

- [7] Xilinx Inc. LogiCORE IP endpoint block plus v1.14 for PCI express[EB/OL]. 2010[2012-04-05]. <http://www.xilinx.com/support/>.