# 高速红外视频处理系统的设计研究

王 厚, 顾国华, 钱惟贤, 陈 钱, 徐富元

(南京理工大学 电光学院, 江苏 南京 210094)

**摘要:** 由于红外地面弱小目标的检测与跟踪技术中, 处理的数据量大, 运算算法复杂, 因此红外视频处理系统要求对数据信息有足够高的吞吐量和处理速度。DSP 在数据的复杂算法运算处理方面有明显的优势, 而 FPGA 更利于实现时序逻辑算法, 所介绍的红外视频处理系统就将 DSP 模块作为核心处理器来完成红外地面弱小目标图像的检测与跟踪算法, FPGA 模块则作为协处理器完成图像接收、预处理、时序控制等功能, FPGA 控制 ARM 模块显示图像处理结果, 形成高效处理图像数据的系统, 该系统通过实践取得了较好的检测跟踪效果。

**关键词:** 红外地面弱小目标; 红外视频处理系统; DSP; FPGA

中图分类号: TN21

文献标识码: A

文章编号: 1001-8891(2013)07-0404-05

## Design Research of High-speed Infrared Video Processing System

WANG Hou, GU Guo-hua, QIAN Wei-xian, CHEN Qian, XU Fu-yuan

(College of Electric & Optic, Nanjing University of Science and Technology, Nanjing 210094, China)

**Abstract:** Infrared video processing system has a sufficiently high throughput and processing speed of the request to the data information, because of the processing of large volumes of data and complex arithmetic algorithm in the infrared ground little target detection and tracking technology. DSP has a distinct advantage in the complex arithmetic operations of the data processing, while FPGA is more conducive to the realization of the temporal logic algorithm, so the infrared video processing system described in this article will be DSP module as the core processor to complete the image of infrared ground little target detection and tracking algorithms, FPGA module as a coprocessor to complete the image receiving, pre-processing, timing control function, FPGA controls the ARM module to display the results of the image processing, to form a highly efficient system for processing image data, this system achieved better detection and tracking results through practice.

**Key words:** infrared ground little target, infrared video processing system, DSP, FPGA

## 0 引言

红外地面弱小目标的检测与跟踪技术在人工智能、自动控制、军事等领域有广泛的应用, 是近年来研究的热点和难点。红外地面弱小目标的可用信息少, 信噪比低, 处理算法复杂, 这就要求红外视频图像处理系统能同时处理大量的数据, 又拥有很高的数据传输处理速度, 并且系统的体积、功耗和稳定性也都有严格的要求。目前, 对于 DSP+FPGA 图像处理系统的研究已经有了一定的成果, 传统的基于 DSP 和 FPGA 的图像处理平台系统<sup>[1]</sup>, 包括图像采集模块, 实时显示控制模块, 和图像数据的分析处理模块, 满

足实时性要求。但是, 由于不同的算法流程对软硬件资源的需求不同, DMA 通信对专有硬件有很强的依赖性<sup>[2]</sup>, 本文改进的图像处理平台系统在执行对算法流程有特定要求的红外地面弱小目标的检测与跟踪任务时, 主要依据改进的自适应混合高斯背景更新算法的需求, 在软硬件资源分配和目标检测与跟踪算法上有所改进。

本文提出了针对红外地面弱小目标的检测与跟踪要求改进的 DSP+FPGA 红外视频处理系统, 该系统具有图像采集、图像滤波、图像配准、目标检测和航迹跟踪等功能, 并且可以将图像处理结果进行显示。该系统旨在实现独立红外视频处理, 可以对图像处理

过程执行本地控制或远程控制,高速传输图像数据,提高图像处理数据量和处理速度,针对红外地面弱小目标的特殊特点,运用改进的滤波和角点检测等预处理算法,再运用改进的目标检测和跟踪算法以达到较好的检测与跟踪效果。

## 1 系统结构

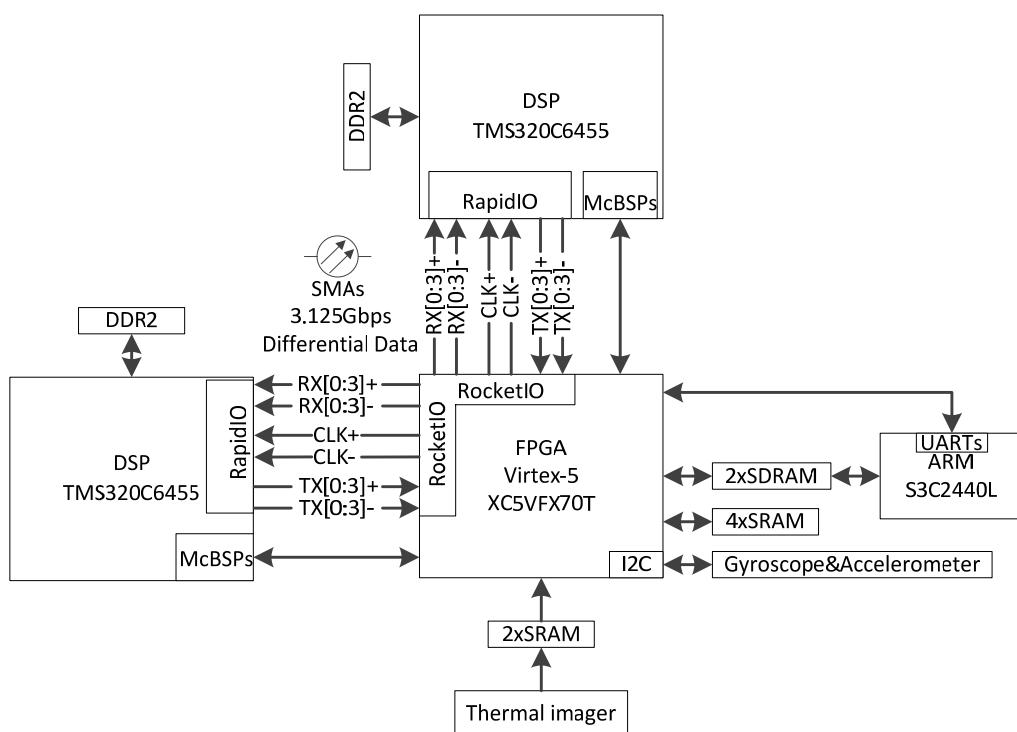

在本文提出的 DSP+FPGA 红外视频处理系统中, FPGA 采用了 Xilinx 公司 Virtex-5 系列的 XC5VFX70T 型号,该型号 FPGA 内置大量 IP 硬核系统级模块,满足具备高级串行连接功能的高性能嵌入式系统的要求,DSPs 运用 TI 公司的 TMS320C6455 ZTZ DSP 芯片作为核心处理器,ARM 的主芯片为 Samsung 公司型号 S3C2440L 的 32 bit CMOS 微处理器,DDR2 和多片 SRAM 有效解决资源不足的问题<sup>[3]</sup>。系统中 FPGA 和 DSP 之间利用 SMAs 光纤差分对进行通信,形成高数据吞吐量的无缝接口,数据传输使用 SRIO 协议,理论上其速率可达 3.125 Gbps。系统中采用双 DSP 进行分布式处理,使主体算法分散在双 DSP 上进行,比单 DSP 数据处理的系统性能更高<sup>[4]</sup>。本系统在总线隔离状态下可成为三核系统,具有强大的重构性,奠定了复杂算法在系统中实现的基础。该系统工作流程为, FPGA 模块先从热像仪接收原始图像信号,实现图像采集功能。两片 DSP 从 FPGA 处取得图

像数据和控制信息,分别执行目标检测算法和轨迹跟踪算法,在完成复杂运算后将所得结果数据和速度返回给 FPGA。FPGA 接收来自 ARM 模块人机界面输入的数据信号和控制命令,最后,ARM 模块接收 FPGA 传来的数据处理结果以实现显示功能。系统硬件结构如图 1 所示,其中 FPGA 模块还要实现图像的预处理和全系统时序控制功能<sup>[5]</sup>。

## 2 系统模块

### 2.1 基于 DSP 的图像算法模块

本文系统中使用 DSP 的 Serial RapidIO 接口进行图像数据交换, RapidIO 作为高带宽外设接口,通过 DMA 总线的存储和寻址以硬件方式来完成数据交换过程,当 FPGA 想要向 DSP 中写数据时,无需 CPU 产生中断,或使用 EDMA 功能, FPGA 将打包成每包 256 B 的图像数据,以 SRIO 协议传输给 DSP。DSP 读取 5120 包数据为 1 帧图像数据后进行处理。DSP 的外设包括 2 片 DDR (MT47H64M16BT, 64 M×16 bit), 1 片 Flash (AM29LV033C, 4 M×8 bit)。

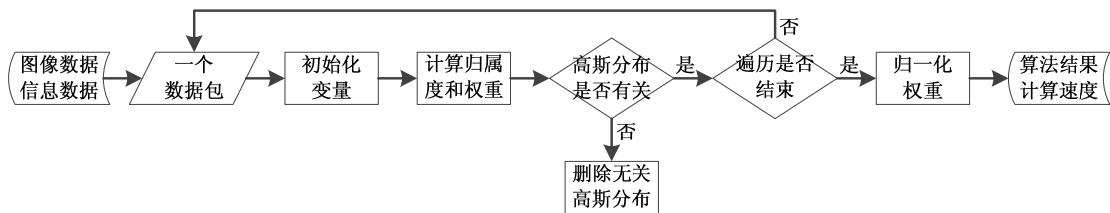

该系统在执行目标检测算法的 DSP 中,执行一种改进的自适应混合高斯模型的背景更新算法,算法逻辑如图 2 所示,其初始化参数有学习因子  $\alpha$ , 混合模型中高斯分布的最大个数  $N$ , 马氏距离参数  $T_\sigma$ , 高斯分布初始化方差  $V_0$ 。

图 1 系统硬件结构框图

Fig.1 System hardware structure diagram

图 2 背景更新算法逻辑框图

该算法的执行过程为,首先 DSP 对接收到的每帧数据图像的每个像素建立多个高斯分布表征的混合高斯模型,取前  $N$  个高斯分布生成初始化背景,用其余的高斯分布依次更新初始化背景的参数,计算每个高斯分布对应当前图像的权重、学习因子、均值、方差和迭代因子,得到每个高斯分布的归属度  $o_n^{(t)}(x)$ 。用  $x^{(t)}$  表示图像中某个位置在时间为  $t$  的像素灰度值,令  $c_T = c/T = N/(2T)$ ,  $\mu_n^{(t)}$  和  $\sigma_n^{(t)}$  分别为高斯分布的均值和方差,  $\omega_n$  表示第  $n$  个分布的权重,  $\sum_{n=1}^N \omega_n = 1$ , 则每个高斯分布的均值和方差为:

$$\hat{\mu}_n^{(t+1)} = \hat{\mu}_n^{(t)} + (1+t)^{-1} \frac{o_n^{(t)}(x^{(t+1)})}{\hat{\omega}_n^{(t)}} \Delta \hat{\mu}_n^{(t)} \quad (1)$$

式中:  $\Delta \hat{\mu}_n^{(t)} = x^{(t+1)} - \hat{\mu}_n^{(t)}$ 。

$$\hat{\sigma}_n^{(t+1)} = \hat{\sigma}_n^{(t)} + (1+t)^{-1} \frac{o_n^{(t)}(x^{(t+1)})}{\hat{\omega}_n^{(t)}} \Delta \hat{\sigma}_n^{(t)} \quad (2)$$

式中:  $\Delta \hat{\sigma}_n^{(t)} = (\Delta \hat{\mu}_n^{(t)}) (\Delta \hat{\mu}_n^{(t)})^T - \hat{\sigma}_n^{(t)}$ , 由此可得递归更新等式:

$$\hat{\omega}_n^{(t+1)} = \hat{\omega}_n^{(t)} + (1+t)^{-1} \left( \frac{o_n^{(t)}(x^{(t+1)})}{1-Mc_T} - \hat{\omega}_n^{(t)} \right) - (1+t)^{-1} \frac{c_T}{1-Mc_T} \quad (3)$$

再根据每个高斯分布的权值删除与实际背景模型无关的高斯分布,最后归一化权重得到结果数据。若图像数据不符合混合模型中的任何高斯分布,则需要建立新的高斯分布<sup>[6]</sup>。然后利用更新后的高斯分布建立背景模型,其中不断调整更新速率的大小。图像点与背景模型中的某个高斯分布匹配,则该点为背景点,否则该点是目标点。

## 2.2 基于 FPGA 的图像预处理模块

本文系统中使用 FPGA 的 RocketIO 接口进行图像数据交换, RocketIO GTP 是 Xilinx Virtex-5 系列提供的用于高速串行互联的 SERDES 硬核<sup>[7]</sup>, 线速率范围为 100 Mb/s 到 3.75 Gb/s。FPGA 的外设包括 6 片 SRAM

Fig.2 Background update algorithm logic diagram

(IS61NLP25636A, 256 k × 36 bit), 用于存储图像数据,并为后续图像处理提供数据,同时视频图像采集模块要求数据能够连续,SRAMs 使用乒乓存储方式为其提供帧缓冲,当 FPGA 从一片 SRAM 中接收一帧数据时,另一片 SRAM 正在从热像仪接收下一帧数据,这种乒乓存储方式以空间换取时间<sup>[7]</sup>,有效提高数据传输速度。

本文系统的 FPGA 处理模块中要实现改进的中值滤波算法和 Harris 角点检测算法。本系统采用 3×3 窗口与 5×5 窗口相结合的中值滤波方法。FPGA 的 36 kb 真双端口 RAM 模块资源可以编程为从 36 kb × 1 到 512 kb × 72 各种深度和宽度配置,36 kb 的真双端口 RAM 模块有 148 个。因此采集图像时以 320 × 16 bit 的 5 个双口 RAM 和 5×5 个触发器形成的 5×5 模板进行采集,5 行 5 列的图像数据先取中间的 3 行 3 列进行中值滤波,得到灰度值的最小值、最大值和中值。求取过程为先对 3×3 矩阵的每行进行升序排列,再对其每列进行升序排列。由此矩阵的第 1 行 1 列元素即为最小值,第 3 行 3 列元素即为最大值。而灰度值的中值为第 1 行 3 列、第 2 行 2 列、第 3 行 1 列这 3 个元素中的中值。如果由 3×3 窗口得到灰度值的中值不大于最小值或不小于最大值,则将计算窗口扩展为 5×5 窗口,计算灰度值的最小值、最大值和中值。再次得到的中值如果大于最小值且小于最大值,则认为计算得到中值。否则,就取 5×5 模板位置的中心点的灰度值为中值。本系统采用的 Harris 角点检测算法是,使用 5×5 模板得到的图像数据,与不同权值的高斯模板和微分模板先后进行卷积,前 5 个尺度图像由原图高斯卷积得到,后 5 个尺度图像由前 5 个高斯卷积得到,求得每个点的尺度空间响应值和位置空间响应值,经过 10 个 FIFO 并行缓存,如果点的尺度空间响应值和位置空间响应值均大于阈值,且大于相邻两层对应点的尺度空间响应值,则判定此点为 Harris 角点。

## 2.3 基于 ARM 的系统显示和人机界面模块

本文系统中,ARM 模块的外设有 2 片 SDRAM (K4S561632C-TC75, 16 M × 16 bit),用在以乒乓存储的方式<sup>[8]</sup>从 FPGA 模块接收图像数据处理结果,并有 2 个 RS232 串口和 FPGA 模块进行控制通信。ARM 模

块有一个 4.3 寸 LCD 触摸屏, 在 Linux 系统下生成人机界面, 具有选择执行目标检测或航迹跟踪的圆钮选择控件, 选择本地控制或通过网络远程控制的控件, 算法参数设置的文本框, 和可以显示系统处理结果的图像显示框。

### 3 系统测试

#### 3.1 测试步骤

1) 系统上电, 热像仪开启。通过热像仪, 该系统接收到  $320 \times 256$ , 16 bit, 50 帧/s 的红外视频灰度图像。

2) 开启 ARM 模块人机界面, 进行系统工作设置。控制模式选择“本地控制”, 参数设置的预处理滤波方式设为“中值滤波”, 在“中值滤波”方式下不用设置阈值, 算法选择“目标检测”, 背景更新算法初始化参数中, 学习因子  $\alpha$  设为“0.1”, 混合模型中高斯分布的最大个数  $N$  设为“3”, 马氏距离参数  $T_o$  设为“2.5”, 高斯分布初始化方差  $V_0$  设为“10”。

3) 在 ARM 模块人机界面上点击“开始”命令按钮, 系统初始化并开始工作。

4) 通过 ARM 模块人机界面上的系统运行流程监控框可以知道系统执行数据处理的详细过程。

5) 当数据处理完成后, 经过处理后的图像在 ARM 模块人机界面上显示。

6) 如果想要继续处理图像, 可以点击 ARM 模块人机界面上的“继续”命令按钮。

#### 3.2 测试结果

1) 测试中 ARM 人机界面如图 3 所示。

2) 系统性能分析如下:

本文设计的 DSP 和 FPGA 红外视频处理系统重点针对红外地面弱小目标的检测和跟踪算法要求进行设

计, 对传统的基于 DSP 和 FPGA 的图像处理平台系统进行了改进。

本文设计的系统中, FPGA 处理模块采用 123 MHz 的时钟进行算法运算, 执行改进的中值滤波算法和 Harris 角点检测算法所用的时间约为 2 ms, 其他操作产生的延迟少于 2 行 4 个像素时钟, 即 516 个像素时钟的延迟  $[516/(125 \times 10^6)]$  s, 约为 4.128  $\mu$ s。

本文设计的系统中, DSP 处理模块和 FPGA 处理模块之间的通信采用 SMAs 光纤接口, DSP 的 RapidIO 接口 (3.125 Gbps) 和 FPGA 的 RocketIO 接口 (3.75 Gbps) 的传输时延  $[(320 \times 256 \times 16 \times 50)/(3.125 \times 10^9)]$  s, 约为 0.42 ms, 满足系统高速数据吞吐量的要求。由于 DMA 通信对专有硬件有很强的依赖性, DSP 和 FPGA 之间使用 SRIO (Serial RapidIO) 接口协议, 大大提高了 DSP 和 FPGA 之间的互联性能, 即使由于相机的数据吞吐量限制, 接口实验测试也得到了约为 1.7 Gb/s 的传输速率。本文设计的图像处理系统中, 图像数据以数据包的形式进行传输, SRIO 数据包最大有效载荷长度为 256 B, 打包效率可以由文献<sup>[9]</sup>中的 79% 提高到 92% 左右。每帧图像传输数据包的次数为 5120 次, 时间约为 4.5 ms, 为算法预留 15.5 ms 的时间。因此本文设计的图像处理系统有很快的传输速度, 软件开销低, 针对红外地面弱小目标的检测和跟踪的需求有明显的优势。

本文设计的系统中, TMS320C6455 DSP 的 DDR2 接口最大带宽为 17.066 Gb/s, 每片 DSP 的 DDR2 可用存储为 128 MB, 接口带宽 32 bit, 地址 0xE0000000~0xE8000000, DDR2 时钟 250 MHz, WE#信号为 H 时 READ, 为 L 时 WRITE。DSP 传输速率的等效频率为 667 MHz, 目标检测模块中缓存及处理部分总共产生的延迟小于 18 行 34 个像素时钟, 大概为 4642 个像素

图 3 ARM 人机界面

Fig.3 ARM man-machine interface

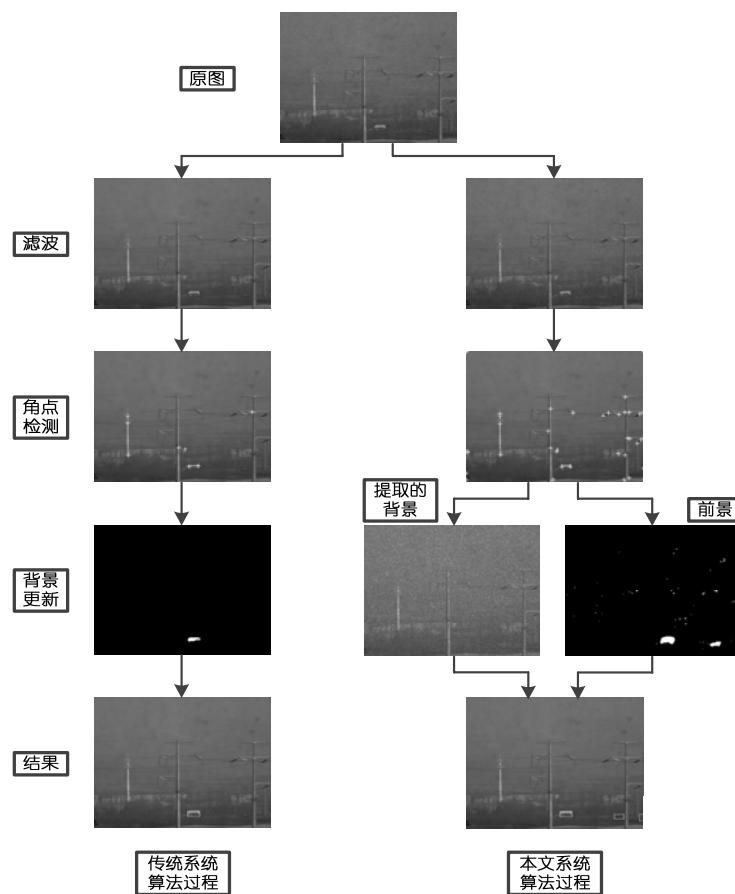

时钟的延迟 $[4642/(667 \times 10^6)]$  s, 约为 6.69  $\mu$ s。DSP 执行目标检测算法, 经实验测试 824 帧图像耗时 117 s, 当背景模型建立后每帧图像算法耗时约为 17 ms。本文设计的图像处理系统的算法和传统算法仿真结果对比如图 4 所示, 因此本文设计的图像处理系统能有效执行改进的自适应混合高斯分布背景更新算法, 针对红外地面弱小目标的检测和跟踪有明显的优势。

## 4 结论

本文介绍的 DSP 和 FPGA 联合组成的红外视频

处理系统, 旨在针对红外地面弱小目标的检测和跟踪算法的需求分离运算任务, 有效发挥各硬件的运算优势, 提高了系统图像数据处理的能力。对于算法而言, 在 FPGA 处理模块完成了改进的中值滤波算法和 Harris 角点检测算法, DSP 处理模块提供的软硬件资源满足了改进的自适应混合高斯背景更新算法的要求, 充分发挥两个处理器的优势<sup>[10]</sup>, 组成了小型便携、可独立运行的图像处理平台, 具有运算速度高, 调试方便等优点, 并且该系统通过实践取得了较好的检测跟踪效果。

图 4 本文系统与传统系统算法对比

Fig.4 Comparison algorithm between system and traditional system

## 参考文献:

- [1] 章奇. 基于 DSP+FPGA 架构视频处理系统设计及其实现[D]. 北京: 中国科学院研究生院, 2006.

- [2] 张峰, 任国强, 吴钦章. 基于 SRIO 的高速图像串行传输系统设计[J]. 光电工程, 2010, 37(10): 89-92.

- [3] 苏海冰, 吴钦章. 用 SDRAM 在高速数据采集和存储系统中实现海量缓存[J]. 光学精密工程, 2002, 10(5): 462-465.

- [4] 李飞飞, 刘伟宁, 孙海江. 基于 FPGA+DSP 的红外弱小目标检测与跟踪系统设计[J]. 激光与红外, 2009, 39(4): 450-453.

- [5] 王平, 高阳, 王林泓, 等. 基于 DSP 与 FPGA 的实时电能质量监测终端系统[J]. 电力系统保护与控制, 2012, 40(12): 125-129.

- [6] 王敏, 郑嘉豪, 王金宝. 基于 DSP 车辆视频检测背景更新算法[J]. 电子科技, 2012, 25(5): 130-132.

- [7] 张天序, 江浩洋. 基于 FPGA 技术的板间 DSP 高速数据通道 Link 口的设计[J]. 微电子学, 2004, 34(5): 543-546.

- [8] 王永翔, 宋术全, 杨宁. 变流器数字控制系统中基于 IP 软核的 DSP, MCU 和 FPGA 芯片间的数据通信技术[J]. 中国铁道科学, 2012, 33(1): 133-138.

- [9] 陆军, 高乐, 刘涛. 基于 DSP 和 FPGA 的全景图像处理系统设计与实现[J]. 嵌入式技术, 2012, 38(6): 24-30.

- [10] 朱明, 鲁剑锋. 基于 DSP+FPGA 结构图像处理系统设计与实现[J]. 计算机测量与控制, 2004, 12(9): 866-869.