# 向数字化发展的红外焦平面阵列

王忆锋, 陆剑鸣

(昆明物理研究所, 云南 昆明 650223)

**摘要:** 在过去数年里, 红外焦平面阵列(FPA)取得了显著进步, 近来的研发重点已经集中到硅读出集成电路(ROIC)上, 帧频增加、引入新型的信号处理功能是该领域的重要进展。因为优于具有模拟信号输出的探测器, 具有数字信号输出的FPA备受关注。数模转换器(ADC)在芯片上的实现是数字FPA的基础, 片上ADC有三种结构, 即芯片级ADC、列级ADC和像元级ADC。主要通过对部分有关英文学术资料的归纳分析, 介绍了数字化FPA的发展动向和趋势。

**关键词:** 数字化FPA; 读出集成电路; 红外成像系统; 模数转换器

中图分类号: TN362 文献标识码: A 文章编号: 1001-8891(2013)04-0195-07

## Toward Digitization in Infrared Focal Plane Array

WANG Yi-feng, LU Jian-ming

(Kunming Institute of Physics, Kunming 650223, China)

**Abstract:** Over the past several years, significant advances in infrared focal plane array(FPA)development have been achieved. Latest developments have been focused on the silicon readout integrated circuit(ROIC). Increasing of frame rate, new types of signal processing functions are an important progress in this field. A FPA with a digital signal output has attracted a lot of attention due to its advantages over detectors with analog signal outputs. The realization of analog to digital converter(ADC) on chip is the base of digital FPA. There are three on-chip ADC architectures, i.e., chip-level ADC, column-level ADC and pixel-level ADC. Mainly by summarizing and analyzing of some related references published in English, the status and trends of digital FPA were presented in this paper.

**Key words:** digital FPA, readout integrated circuit, infrared imaging system, analog-to-digital converter

## 0 引言

以往红外焦平面阵列(FPA)技术研发的重点主要集中在探测器材料、器件等方面<sup>[1]</sup>。在过去十多年里, 国外相关产品已经达到了极高的质量水平<sup>[2]</sup>, FPA器件正向数字化发展<sup>[3]</sup>。在芯片上实现的模数转换器(ADC)是FPA数字化的基础。从发展过程来看, ADC是与数字信号处理技术一起引入红外系统的, 只是以往多在读出(集成)电路(ROIC)芯片外围、在电路板级实现, 称为(芯)片外(off-chip)ADC。当ADC在ROIC芯片内部实现时, 即可构成数字ROIC<sup>[4-7]</sup>, 或称为(芯)片上ADC(on-chip ADC)<sup>[8]</sup>。CMOS工艺技术的发展, 不仅使片上ADC成为可能, 还可以将ROIC外面完成的某些数字信

号功能引入ROIC芯片, 形成数字FPA或智能FPA<sup>[9]</sup>。数字ROIC+FPA即形成数字(像元)FPA(digital-pixel FPA, digital FPA)<sup>[10-14]</sup>。这一概念还可以进一步外延, 例如有关厂家提供的制冷型探测器组件一般是探测器-杜瓦-制冷机(Detector-Dewar-Cooler, DDC)的集成件, 引入数字ROIC后即变成数字DDC(D<sup>3</sup>C)<sup>[15]</sup>。

根据ADC在ROIC所处位置或层次, 片上ADC又可分为芯片级ADC、列级ADC和像元级ADC<sup>[16]</sup>。数字FPA具有许多优点, 例如对于引入的外部噪声具有较高的免疫性、克服处理电子学的非线性问题、对于外部环境条件例如温度的变化不太敏感、以及残余非均匀性(residual non uniformity, RNU)具有较长的稳定性等<sup>[17]</sup>。本文主要以部分英文学术资

收稿日期: 2013-01-11; 修订日期: 2013-03-04。

作者简介: 王忆锋(1963-)男, 湖南零陵人。1984年毕业于北京工业学院(今北京理工大学)计算机系, 工学士。高级工程师。2000年8月~2001年6月在美国内布拉斯加大学林肯分校计算机系做国家公派访问学者。目前主要从事器件仿真研究。E-mail: wangyifeng63@sina.com。

料为基础,介绍了数字FPA的若干发展动向。

## 1 ADC的一般性描述

ADC的作用是将时间连续、幅值连续的模拟信号转换为时间离散、幅值离散的数字信号,其基本功能包括采样、保持、量化和编码。在实际电路中,这些过程有的是合并进行的,例如,采样和保持,量化和编码往往都是在转换过程中同时实现的。

在一定的时间间隔内,数字信号只取有限数目的数值之一,因而可用二进制数来表示,所用二进制数的位数或长度n称为分辨率或精度。高精度是ADC的发展趋势之一。为了适应噪声与信号水平之间增加的动态范围,需要高精度ADC<sup>[18]</sup>。文献中提到的FPA/ADC精度有15位<sup>[17,19]</sup>、16位<sup>[20]</sup>。ADC分辨率直接与FPA的动态范围DR(=2<sup>n</sup>)相联系。动态范围还可以用分贝(dB)来表示,分贝值等于 $20 \times \lg(DR)$ ,于是120 dB的动态范围对应于20位的ADC分辨率。文献[21]分析了放大器增益、带宽、电容匹配、噪声和偏置电压等因素对于ADC精度的影响。

ADC完成一次从模拟转换到数字所需时间称为ADC的转换速度,其中没有包括采样/保持所耗的时间。一般将转换时间大于300 μs的ADC称为低速ADC;转换时间为1~300 μs的ADC称为中速ADC;转换时间小于1 μs的ADC称为高速ADC。

转换时间与采样/保持等环节所耗的时间之和称为整个ADC的采样速度;因此采样速度一般低于转换速度。采样速度的倒数称为采样频率,它是指ADC每秒能完成多少次的采样,用赫兹(Hz)来表示。

在影视技术中,单幅静止的图像称为一帧。每秒钟刷新的帧数称为帧频。这些概念可以沿用到FPA。例如,一组完整的FPA数据称为一帧或全帧(full frame)<sup>[22]</sup>,其中所开的窗口区域称为子帧(sub frame)。快速连续地显示或处理各帧,即可从目标在各帧中所处位置关系推断其运动速度及方向。FPA的帧频与ADC的分辨率两者之间是相互制约的。文献[17]介绍可以通过外部电路控制ADC分辨率,例如15位ADC可以120 Hz的帧频全帧工作,13位ADC可以200 Hz的帧频全帧工作。

帧频因应用不同而异。30~60 Hz帧频对于目视显示已经足够<sup>[18]</sup>;对于面向快速运动目标的应用,为了在帧平均之前完成图像配准,需要较高的帧频<sup>[23]</sup>。例如,导弹预警、导弹导引头等应用则要求帧频在300 Hz以上<sup>[11]</sup>;文献[24]更指出对于此类

应用要求FPA的动态范围>120 dB,帧频在1000 Hz。法国Sofradir公司的一款MWIR/MCT器件可以做到140 Hz的全帧读出<sup>[22]</sup>;德国AIM公司MCT器件的帧频已可做到800 Hz以上<sup>[25]</sup>。不难预料对于高超音速飞行器的预警<sup>[26]</sup>需要更高的帧频。由于输出驱动功率与帧频成正比,故高帧频将使芯片功耗增加,相应地进一步引起低温制冷机功耗的增加。一种解决方法是将高帧频限制在一个可处于任意位置、例如64×64个像元构成的小窗口内<sup>[18]</sup>。文献[27]报道,像元级ADC可以达到1000 Hz以上的帧频。另外,通过引入开窗功能来减少读出时间,可以提高所选窗口的帧频<sup>[18]</sup>。

FPA/ROIC的原始数据率可以表示为:

$$\text{原始数据率} = \text{FPA 像元数} \times \text{帧频} \times \text{ADC 分辨率}$$

例如,对一个帧频60 Hz、14位ADC分辨率、1280×720的FPA,其原始数据率为:

$$1280 \times 720 \times 60 \times 14 = 774144000 = 774 \times 10^6 \\ = 774 \text{ Mbps} = 0.77 \text{ Gbps}$$

bps(bits per second)表示每秒可传输的位数。

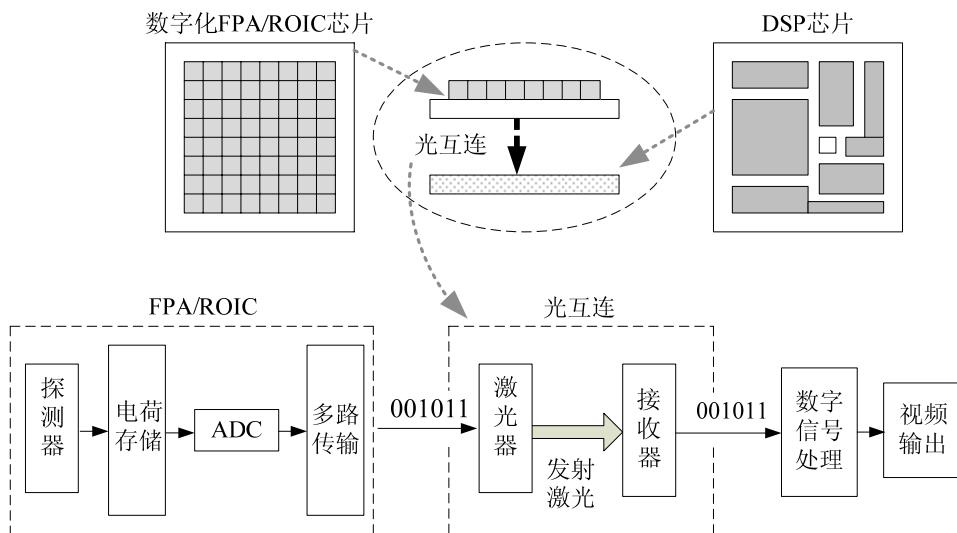

当FPA数据率较高时,已不能只用一个通道来送出数据<sup>[9]</sup>。特别地,高帧频与高清晰度结合产生的Gbps量级的数据率可能构成数据传输瓶颈。缓解该瓶颈的途径之一是用铜引线互连替代铝引线互连。另一方面,即使是用铜连线,其数据传输率仍受寄生电阻、电感和电容等因素的影响;引线越长越细,数据传输率越低,这是由于电互连在物理性能方面的局限性所造成的。由于光波的波长比波长最短的无线电波还要小4个数量级,因而具有更大的传输能力。如图1所示,最终的解决方案是引入光互连技术<sup>[28]</sup>,开发光电混合的集成电路,即类似于把晶体管、电子开关等装置集成在一个IC芯片上一样,将光子开关、激光器、光纤、探测器等集成在一个光路上。光互连可在芯片内、芯片间或电路板之间实现。如同IC电路中的电子开关一样,光互连的核心之一是光子开关。光子开关一方面必须具有良好的性能,另一方面必须能够集成为大规模开关矩阵。在各种形式的光子开关中,微光机电系统(MEMS)光子开关是最具发展前景的光子开关之一。MEMS光子开关通常是采用在半导体基片上构造一个微反射镜阵列,通过反射镜的运动完成开关动作,具有与IC工艺兼容,易于量产和集成等优点。在激光器方面,基于布拉格反射器制备的垂直共振腔表面激光器(VCSEL)是一个很好的选择,其出光方向垂直衬底,可实现高密度二维面阵的集成。VCSEL光源可调变频率高达数GHz,相应的传输

图1 利用光互连解决数据传输的瓶颈问题

Fig.1 Solving the bottleneck of data transmission with optical interconnects

速率可达 Gbps 量级。此外,它还具有阈值低、稳定性好、寿命长等优点,非常适合于在芯片与芯片之间甚至在芯片的各个部分之间实现光互连。

按工作原理的不同,ADC可分为直接ADC和间接ADC两类。直接ADC将模拟信号直接转换为数字信号,因而具有较快的转换速度,其典型电路有并行比较型ADC、逐次比较型ADC等。间接ADC则是先将模拟信号转换成某一中间量(时间或频率),然后再将中间量转换为数字信号,故转换速度较慢;典型电路是双积分型ADC、电压频率转换型ADC等。根据不同的应用要求,每一类ADC都有相应的优化设计方法。

根据采样定理,如果采样频率 $f_s$ 大于有限带宽信号 $x_a(t)$ 带宽 $f_0$ 的2倍,即 $f_s > 2f_0$ ,则可以保存模拟信号的全部信息;任何更高的采样速率也将保存模拟信号的全部信息。量值 $2f_0$ 称为Nyquist频率。如果采样频率远大于Nyquist频率(至少是16倍,一般会更多),这种情况称为过采样(over sampling);如果采样频率只比Nyquist频率大几倍,则称为多重采样(multiple sampling)。如果采样频率小于Nyquist频率,则称为欠采样(under sampling)。这几种采样方式在ADC中均有应用。

ADC由电阻网络和模拟开关等构成,其工作有一定的功耗。高速ADC功耗较大,结构复杂、占用面积较大;低速ADC则相反,功耗较小,结构简单、占用面积较小。对于制冷型FPA来说,ADC要与FPA一起放在低温环境下,因此自然希望ADC功耗越小越好。对于用各种技术工艺制备的常规ADC,文献[29, 30]介绍了采样频率、分辨率与ADC

功耗之间的统计关系。对于用0.5 μm工艺实现40 MHz采样频率、15位分辨率的情况(这是高端制冷型红外探测器信号处理器的典型特征),ADC平均功耗为1.3 W;因此对于一款典型的制冷效率为4%的Stirling制冷机,其功耗为32 W,这对于常规的红外成像系统来说是不可接受的<sup>[17]</sup>。

高速(即高转换速度或高采样频率)、高分辨率(即高转换位数)和低功耗是ADC的发展趋势。但是ADC的速度、精度和功耗三者之间是相互矛盾、相互制约的;提高速度,自然要牺牲分辨率和功耗;提高精度或分辨率,要牺牲转换速度和功耗;降低功耗,则要相应降低速度和分辨率。它们的选择与权衡必须从ADC电路结构入手,同时又依赖于制造工艺的参数匹配。

有多种ADC算法可供FPA使用<sup>[20,31]</sup>。如果说ADC算法是对ADC工作原理的描述,那么ADC电路结构则是该算法在硬件上的体现。具体结构的选择与系统设计密切相关。

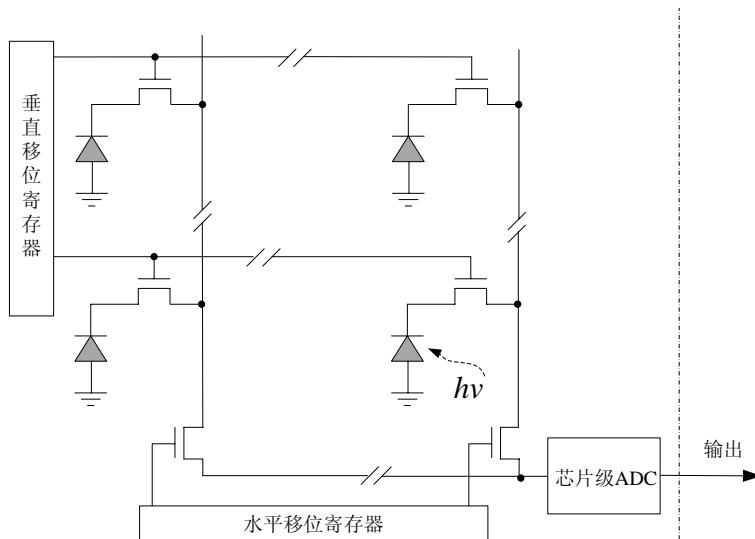

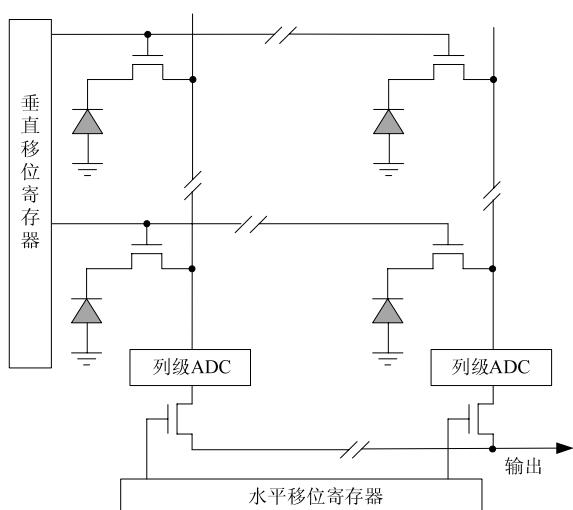

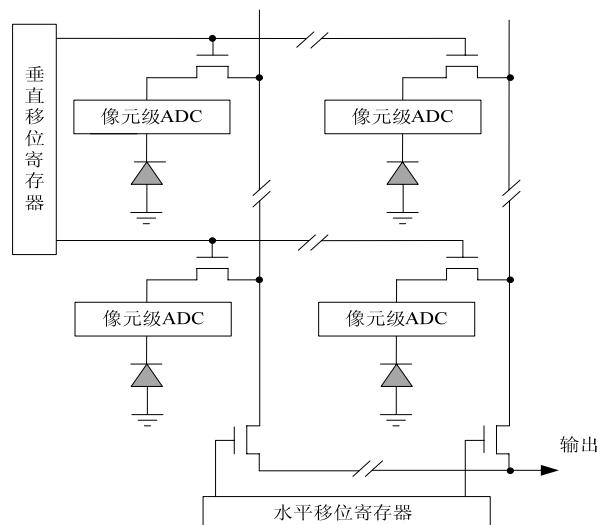

## 2 片上ADC的特点

与一般的ADC相比,片上ADC的特殊性在于它不是一块单独的芯片,而是在FPA已有的ROIC芯片内新增ADC功能,是一种“嵌入”或“隐性的ADC。根据ADC所在位置,片上ADC又可分为芯片级ADC、列级ADC或像元级ADC<sup>[16]</sup>,如图2~图4所示。

设想要在一个指定的时间段得到FPA的数字信号。芯片级ADC因为整个FPA使用一个ADC,每个像元的输出都要经过该ADC,相当于串行工作,

图 2 芯片级 ADC, 整个 FPA 使用一个 ADC

Fig.2 Chip-level ADC with only one ADC for the whole FPA

图 3 列级 ADC, 每列像元配置一个 ADC

Fig.3 Column-level ADC with an ADC per each column

显然要求配用高速 ADC; 列级 ADC 为每一列像元配置一个 ADC 逐列转换, 属于半并行工作, 故对速度的要求有所降低, 可用中速 ADC。

在像元级 ADC 中, 即每一个像元配置一个 ADC(其优点是当数字数据从 FPA 读出时没有信号衰减发生<sup>[9]</sup>), 各 ADC 同时并行工作, 故可以采用低速 ADC, 通过以大量低速 ADC 的并行工作来获得一个高速 ADC 的效果。也可以选择若干(例如 4 个<sup>[10,32]</sup>) 像元为一组共用一个低速 ADC。文献[32]报道, 将每 4 个相邻像元作为一组, 共用一条读出线和一个积分电容。这样处理使得积分电容增加了 6~10 倍; 读出线数量降低了一半, 并且由于拉开了读出线之间的间距, 从而为引入其他信号处理功

图 4 像元级 ADC, 每个像元配置一个 ADC

Fig.4 Pixel-level ADC with an ADC dedicated to each pixel

能留下了空间。

### 3 片上 ADC 的实现

FPA 芯片与 ROIC 芯片有两种整合方式, 一种是通过钢柱互连将 FPA 芯片与 ROIC 芯片合为一体, 称为混合集成<sup>[33]</sup>; 另一种是直接在 ROIC 上制备 FPA, 称为单片集成。混成器件的优点是具有较高的填充因子, 因为探测器可以直接集成在电路上方, 可以对探测器和电路分别进行独立的优化, 故可使器件性能显著改善; 其缺点是器件成本较高, 因为混成有一个相关组装成本的问题<sup>[9]</sup>。但是不管哪种集成, ROIC 芯片面积一般不会超出 FPA 芯片太多。在过去 20 多年里, FPA 像元中心距从 50  $\mu$ m

左右不断缩小<sup>[34]</sup>; 12 μm 中心距现已成为中波和长波红外器件的标准<sup>[35]</sup>; 还出现了 10 μm<sup>[36]</sup>、5 μm<sup>[35]</sup> 中心距的器件。在相同的像元数下, 中心距的减少意味着 FPA 芯片面积变小, 这种变化趋势给片上 ADC 的实现造成了相当大的制约。具体来说, 首先要考虑拟用的 ADC 结构是否可被 FPA 像元中心距所限定的微小空间所容纳; 换言之, 如果地方大, 可用复杂结构; 如果地方小, 可用简单结构, 或者只放入 ADC 结构的主要部分。如果不能容纳, 只能放在片外实现。

形象地讲, 设想有一张 ROIC 版图, 容纳该版图的面积是一定的。如果用粗线条去画该版图, 那么它占用面积就大, 可能刚够放下前置放大器等结构; 如果用细线条去画同样的结构, 可能还有空余面积再放下一个 ADC, 这就是芯片级 ADC; 如果可以放入一排 ADC, 即构成列级 ADC; 如果再用更细小的线条, 并将版图折叠为几层来放, 就可能做到一个像元或者以几个像元为一组配一个 ADC, 即像元级 ADC。这里说的版图折叠实际上就是 IC 设计中的多层布线或立体布线, 而线条粗细则对应于布线所用的线宽。

线宽是指 IC 生产工艺可达到的最小导线宽度, 是表征 IC 工艺先进水平的主要指标。线宽越小, 集成度越高, 在单块芯片上可容纳的元件数目越多,

同时投资强度也越大。各代 IC 工艺的部分特点如表 1 所示<sup>[37]</sup>, 该表反映了当今 IC 产业技术发展的一些特点, 例如, 由于 IC 芯片表面凸凹不平, 多层布线十分困难, 为此需要实现各层金属膜的平坦化。以往所用的各种平坦化技术, 例如化学气相沉积 (CVD) 技术、Etch-back 等很难获得较好的平坦化效果。化学机械抛光 (CMP) 技术具有加工方法简单、加工成本低等优点, 可实现全局平坦化。不使用 CMP 技术一般只能做 2~3 层布线; 利用 CMP 技术以及铜引线, 可实现 10 层以上的多层布线。CMP 和 Etch-back 等几个单项工艺的组合称为大马士革工艺。由于铜比铝具有更低的电阻率、优越的抗电迁移特性和低的热敏感性, 被视为较为理想的引线材料, 是目前 IC 设计和制造中的主流技术。铜互连需要采用大马士革工艺做一层电镀。

大体上可以将 FPA 芯片划属光电子行业, IC 芯片划属集成电路行业。从表 1 所列出各代 IC 工艺所需设备的价格, 可以看到资金密集是两者的共同特点; 而 ROIC 恰好处于两者之间的特殊位置。这些在现实中的反映就是 ROIC 一般为这两个行业分工协作的产品, 即 FPA 业者提出 ROIC 设计, 再交给 IC 业者投片生产。ROIC 的性能主要依赖于实现器件结构的硬件设备(国内 IC 生产设备特别是高端设备对国外依赖度很高)和半导体软件工艺方法。

表 1 各代 IC 工艺的特点

Table 1 Specifications for different generations of IC techniques

| 工 艺                         | 缺 陷/mm <sup>2</sup> | 数 量   |         | 工 艺 结 构 特 点                                                       | 设备价格<br>/百万美元 |

|-----------------------------|---------------------|-------|---------|-------------------------------------------------------------------|---------------|

|                             |                     | 光 刻 版 | 工 艺 工 序 |                                                                   |               |

| 1.4~2.0 μm 线宽<br>1~2 个金属层   | 2~5                 | 8~10  | 40~70   | 局部氧化<br>干法腐蚀                                                      | 7~10          |

| 0.7~1.0 μm 线宽<br>2 个金属层     | 0.7~1.5             | 10~11 | 90~110  | 带有 Hg 435 nm 源的光刻<br>自对准岛                                         | 16~20         |

| 0.5~0.6 μm 线宽<br>3~4 个金属层   | 0.4~0.6             | 12~14 | 120~130 | 化学等离子研磨平坦化<br>带有 Hg 404 nm 源的光刻<br>大角度离子掺杂                        | 30~40         |

| 0.25~0.35 μm 线宽<br>4~5 个金属层 | 0.2~0.3             | 15~17 | 140~150 | 机械化学研磨平坦化<br>带有 Hg 365 nm 源的光刻<br>沟道隔离                            | 80~100        |

| 0.13~0.18 μm 线宽<br>6 个金属层   | 0.05~0.1            | 18~20 | 160~170 | 退变岛<br>自对准硅接触层<br>带有 Kr 248 nm 源的光刻<br>$\varepsilon > 3.9$ 的栅极介电质 | 200~300       |

|                             |                     |       |         | $\varepsilon < 2.7$ 的层间介电质<br>大马士革金属化<br>带有 Ar 139 nm 源的光刻        |               |

基本上是国外产品), ROIC 的功能仅受制于设计者的想象力以及像元空间尺寸的局限性<sup>[2]</sup>。设计方法则有半定制、全定制和逆向之分。半定制正向设计是主流技术, 全定制一般应用在 CPU 等高端产品, 逆向方法一般多应用于军用集成电路的设计。

ROIC 用到的线宽先后有  $1.2\text{ }\mu\text{m}$ <sup>[38]</sup>、 $0.9\text{ }\mu\text{m}$ <sup>[10]</sup>、 $0.6\text{ }\mu\text{m}$ <sup>[39-40]</sup>、 $0.35\text{ }\mu\text{m}$ <sup>[27, 41]</sup> 和  $0.18\text{ }\mu\text{m}$ <sup>[4, 12, 19]</sup> 等。 $0.35\text{ }\mu\text{m}$  线宽工艺在  $30\text{ }\mu\text{m} \times 30\text{ }\mu\text{m}$  面积上可以安排一百多个晶体管<sup>[27]</sup>。中心距较大时可用线宽较大的工艺, 例如对于  $60\text{ }\mu\text{m}$  中心距, 可以用  $1.2\text{ }\mu\text{m}$  线宽的工艺在每个像元位置做一个 ADC<sup>[38]</sup>。目前主流产品线宽为  $0.25\text{ }\mu\text{m}$  (该线宽工艺可以在每个像元下制作一个完整的 16 位 ADC), 先进的已降到  $0.13\text{ }\mu\text{m}$ 。国内通过引进、吸收, 已有  $0.35\text{ }\mu\text{m}$ 、 $0.25\text{ }\mu\text{m}$  线宽的工艺线; 有的企业在设计技术水平方面也达到  $0.13\text{ }\mu\text{m}$ 。 $0.1\text{ }\mu\text{m}$  工艺可引入数百个晶体管<sup>[27]</sup>, 使得原来放在 ROIC 外面完成的一些功能例如 ADC 等以及若干简单的信号处理可以移入 ROIC<sup>[10, 39, 42]</sup>。文献[43]介绍, 将  $2.5\text{ }\mu\text{m}$  线宽 CCD 工艺和  $2\text{ }\mu\text{m}$  线宽 CMOS 工艺组合使用, 可以在  $288 \times 4/\text{MCT/ROIC}$  引入一般要用  $0.8\text{ }\mu\text{m}$  工艺实现的坏像元剔除功能, 此外还可以实现其他所需的大多数功能。文献[44]介绍了 BAE 公司为 FPA/ROIC 研发的一系列先进信号处理结构, 包括 ADC、偏置相减、单像元自动增益补偿、瞬态噪声抑制、坏像元剔除、开窗、空间神经网络处理、亚帧噪声平均等。还可以引入片上图像处理功能<sup>[10, 13]</sup>。

#### 4 关于片上 ADC 的结构选择

片上 ADC 结构需要在综合考虑芯片面积、功耗、速度、精度等因素的基础上折衷选择<sup>[21]</sup>。芯片级 ADC 因为面积不受很强的限制, ADC 类型的选择没有什么限制<sup>[9]</sup>, 多采用中等功耗的高速流水线 ADC 结构<sup>[39]</sup>, 其缺点是高速 ADC 会带来较大功耗。2008 年文献报道的 ADC 最好的功耗水平为<sup>[2]</sup>:  $1\sim 2\text{ mW/MHz/12 位}$ ,  $3\sim 4\text{ mW/MHz/14 位}$ ,  $3\text{ mW/100 kHz/16 位}$ 。另外由于 FPA 与 ADC 之间数据传输的是模拟信号, 不可避免地会引入额外噪声, 使系统性能受到影响。

列级 ADC 可分为单斜率 ADC、双斜率 ADC、逐次逼近 ADC、过采样 ADC 等。过采样 ADC 又称  $\Sigma$ - $\Delta$ 型 ADC, 通常由高阶  $\Sigma$ - $\Delta$  调制器 (例如, 4 阶或更高) 配合一个多位 ADC 和多位反馈 DAC 构成, 其突出优点是在一片混合信号 CMOS 电路上实现 ADC 与数字信号处理技术的结合, 分辨率在  $12\sim$

16 位、甚至可做到 24 位。在过采样 ADC 方案中, 只要有足够的面积可用, 那么使用二阶而不是一阶  $\Sigma$ - $\Delta$ 型 ADC 是一种更优的方案<sup>[9]</sup>。在二阶  $\Sigma$ - $\Delta$ 型 ADC 中, 过采样率可以显著降低<sup>[45]</sup>。文献[42]介绍了一种用于制冷型 FPA (中心距  $25\text{ }\mu\text{m}$ ) 的列级二阶增量  $\Sigma$ - $\Delta$ 型 ADC, 包括滤波器在内的电路用  $0.35\text{ }\mu\text{m}$  CMOS 工艺实现。

由于 IC 制备工艺的随机性, 两个在设计上完全相同的器件在性能上也会呈现出某种程度的随机性失配, 更何况成千上万个一起工作的 ADC。故为了获得较好的成像效果, 像元级 ADC 必须具有良好的均匀性。另一方面, 像元级 ADC 一般要用小线宽工艺才能实现。而随着线宽的减小, ADC 精度也会受到影响。为了解决这一矛盾, 可以速度降低为代价来获得较高的精度, 例如将采样频率提高到过采样的程度, 与此对应的就是过采样 ADC。这种速度降低的代价是可以承受的, 因为现代短通道 CMOS 工艺提供的速度性能经常超过系统需求, 并且这种速度性能随着将来更短通道的获得而持续改善<sup>[9]</sup>。对于一阶电流输入  $\Sigma$ - $\Delta$ 型 ADC, 可以选择仅将  $\Sigma$ - $\Delta$ 型 ADC 的前端可以放入芯片, 因为其  $\Sigma$ - $\Delta$  前端占用面积最小。这种结构的优点是,  $\Sigma$ - $\Delta$ 型 ADC 前端产生数字数据, 不会将噪声引入信号<sup>[9]</sup>。文献[42]认为, 对于高性能及中等规模 FPA, 例如  $320 \times 240$ , 除了功耗较高的缺点以外,  $\Sigma$ - $\Delta$ 型 ADC 是一种有前景的解决方案。

另一种常用的像元级 ADC 结构是多通道位串行 (multi-channel-bit-serial, MCBS) ADC<sup>[46]</sup>, MCBS 结构 ADC 最重要的优点是可以通过多重采样、编程增强动态范围<sup>[16]</sup>。

#### 5 结束语

数字 FPA 有望实现更多的片上信号处理功能, 使杜瓦设计具有更简单的电气接口<sup>[13-14]</sup>, 降低系统成本、复杂性、重量和噪声。引入图像处理功能可以实现智能型 FPA, 这是一个正在深入研究的领域<sup>[9]</sup>。数字 FPA 的发展需要研究新的图像处理算法、体系结构和电路设计, 以满足在功耗、芯片面积和速度等方面苛刻要求<sup>[42]</sup>, 相关工作越早考虑越容易实施<sup>[2]</sup>。片上 ADC 是 FPA 数字化的核心。模拟电路是 ADC 的关键部分。随着相关技术的发展, CMOS 工艺可实现的线宽不断减小, 但是小线宽工艺在带来集成优势的同时也增加了模拟电路的设计难度, 尤其是高性能 ADC 电路。

本文中若干数据和表述取自网络资料, 限于篇

幅未逐一列出,特此说明。

## 参考文献:

- [1] Chen L P, Hewitt M J, Gulbransen D J, et al. Overview of advances in high-performance ROIC designs for use with IRFPAs[C]//*Proc. of SPIE*, 2000, **4028**: 124-138.

- [2] Sprafke T, Beletic J W. High performance infrared focal plane arrays[J]. *Optics & Photonics News*, 2008, **19**(6): 22-27.

- [3] 王忆锋, 唐利斌. 硼镉汞近年来的研究进展[J]. 红外技术, 2009, **31**(8): 435-442.

- [4] Shkedy L, Markovitz T, Calahorra Z, et al. Megapixel digital InSb detector for midwave infrared imaging[C]//*Optical Engineering*, 2011, **50**(6): 061008.

- [5] Tribollet P, Destefanis G. HgCdTe large staring arrays at SOFRADIR[C]//*Proc. of SPIE*, 2007, **6636**: 663603.

- [6] Vial L, Combette A, Gohier D. Latest developments on MCT staring arrays[C]//*Proc. of SPIE*, 2006, **6395**: 63950E.

- [7] Pistone F, Verdet S, Tribollet P, et al. Progress in MCT large staring arrays[C]//*Proc. of SPIE*, 2006, **6295**: 62950K.

- [8] Chen L P. Advanced FPAs for multiple applications[C]//*Proc. of SPIE*, 2002, **4721**: 1-15.

- [9] Joo Y, Park J, Thomas M, et al. CMOS Focal Plane Arrays: A Si CMOS detector array and sigma-delta analog-to-digital converter imaging system[J]. *IEEE Journal of Selected Topics in Quantum Electronics*, 1999, **5**(2): 296-305.

- [10] Brown M G, Baker J, Colonero C, et al. Digital-pixel focal plane array development[C]//*Proc. of SPIE*, 2010, **7608**: 76082H.

- [11] Markovitz T, Pivnik I, Calahorra Z, et al. Digital  $640 \times 512$   $15 \mu\text{m}$  InSb detector for high frame rate, high sensitivity, and low power applications[C]//*Proc. of SPIE*, 2011, **8012**: 80122Y.

- [12] Kelly M, Berger R, Colonero C, et al. Design and testing of an all-digital readout integrated circuit for infrared focal plane arrays[C]//*Proc. of SPIE*, 2005, **5902**: 59020J.

- [13] Decaens G, Zecri M, Maillart P, et al. Ultra-low power ADC on chip for high-performance IR detector[C]//*Proc. of SPIE*, 2009, **7298**: 72983H.

- [14] Fillion P, Dugalleix S, Pistone F, et al. Digital output for high-performance MCT staring arrays[C]//*Proc. of SPIE*, **6206**: 62060U.

- [15] Nesher O, Klipstein P C, Weiss E. Advanced IR detector design at SCD: from  $\text{D}^3\text{C}$  to ABCS[C]//*Proc. of SPIE*, 2004, **5359**: 101-110.

- [16] Gamal A E, Yang D, Fowler B. Pixel Level Processing—Why, what, and how?[C]//*Proc. of SPIE*, 1999, **3650**: 2-15.

- [17] O. Nesher, S. Elkind, A. Adin, et al. A Digital cooled InSb detector for IR detection[C]//*Proc. of SPIE*, 2003, **5074**: 120-129.

- [18] Horn S, Norton P, Cincotta T, et al. Challenges for third-generation cooled imagers[C]//*Proc. of SPIE*, 2003, **5074**: 44-51.

- [19] Bisotto S, Borniol E, Molland L, et al. A  $25 \mu\text{m}$  pitch LWIR staring focal plane array with pixel-level 15-bit ADC ROIC achieving  $2 \text{mK}$  NETD[C]//*Proc. of SPIE*, 2010, **7834**: 78340J.

- [20] Ringh U, Jansson C, Liddiar K. Readout concept employing a novel on chip 16 bit ADC for smart IR focal-plane-arrays[C]//*Proc. of SPIE*, 1996, **2745**: 99-110.

- [21] Pain B, Fossum E R. Approaches and analysis for on-focal-plane analog-to-digital conversion[C]//*Proc. of SPIE*, 1994, **2226**: 208-217.

- [22] Biesczad G, Sosnowski T, Madura H, et al. Image processing module for high-speed thermal camera with cooled detector[C]//*Proc. of SPIE*, 2011, **8012**: 80120L.

- [23] Kavusi S, Ghosh K, Fife K, et al. A  $0.18 \mu\text{m}$  CMOS 1000 frames/sec, 138 dB dynamic range readout circuit for 3D-IC IR focal plane arrays [C]//*Custom Integrated Circuits Conference*, 2006: 229-232.

- [24] Balcerak R, Horn S. Progress in the development of vertically integrated sensor arrays[C]//*Proc. of SPIE*, 2005, **5783**: 384-391.

- [25] Breiter R, Cabanski W A, Koch R, et al. AIM image processing electronics for FPA IR detection modules[C]//*Proc. of SPIE*, 2003, **5074**: 130-137.

- [26] 王忆锋, 余连杰, 马钰. 即时全球打击(PGS)武器早期预警对光电子探测器的需求分析[J]. 激光与红外, 2011, **41**(3): 288-292.

- [27] Kleinfelder S, Hottes A, Fabian R, et al. Focal plane array readout integrated circuit with per-pixel analog-to-digital and digital-to-analog conversion[C]//*Proc. of SPIE*, 2000, **4028**: 139-147.

- [28] Mandl W J, Ennulat R D, Terrill C W, et al. LWIR focal plane with digital readout demonstrating a passive free-space optical readout link[C]//*Proc. of SPIE*, 1999, **3698**: 736-747.

- [29] Kozlowski L J, Vural K, Tennant W E, et al. Progress towards high-performance infrared imaging system-on-a-chip[C]//*Proc. of SPIE*, 2000, **4130**: 245-253.

- [30] Kozlowski L J, Loose M, Joshi A, et al. Low power system-on-chip FPAs[C]//*Proc. of SPIE*, 2002, **4820**: 525-534.

- [31] William J M, Rutschow C. All-digital monolithic scanning readout based on sigma-delta analog-to-digital conversion[C]//*Proc. of SPIE*, 1992, **1684**: 239-246.

- [32] Lee I I. A new readout integrated circuit for long-wavelength IR FPA[J]. *Infrared Physics & Technology*, 2010, **53**(2): 140-145.

- [33] 许娅明, 任华. 320×240 混合式非制冷红外焦平面探测器芯片工艺研究[J]. 红外技术, 2010, **32**(1): 1-5.

- [34] Bercier E, Dessus J L, Manissadjian A, et al. State-of-the-art of mass production: challenges for low-cost and application benefits of high-performances small-pitch IR detectors[C]//*Proc. of SPIE*, 2008, **6940**: 69400I.

(下转第 222 页)

- [8] 宋岩峰, 邵晓鹏, 徐军. 离轴三反镜光学系统研究[J]. 红外与激光工程, 2008, **37**(4): 706-709.

- [9] 刘琳, 薛鸣球, 沈为民. 提高离轴三反射镜系统成像质量的途径[J]. 光学技术, 2002, **28**(2): 181-184.

- [10] 史光辉. 卫星对地观测高分辨率光学系统和设计问题[J]. 光学精密工程, 1999, **7**(2): 16-24.

- [11] 李旭阳, 李英才. 高分辨率空间相机共轴三反光学系统实现形式研究[J]. 应用光学, 2009, **30**(5): 717-723.

- [12] ZEMAX 中文使用手册[S]. 南京: 光研科学有限公司, 2007.

- [13] 王红, 韩昌元. 温度对航天相机光学系统影响的研究[J]. 光学技术, 2003, **29**(4): 452-457.

- [14] 袁涛, 熊衍建, 吴晗平. 空间相机共轴三反红外光学系统设计[J]. 光电技术应用, 2011, **26**(2): 21-26.

- [15] 高明辉, 刘磊, 任建岳. 空间相机反射镜碳化硅材料性能测试[J]. 光学精密工程, 2007, **15**(8): 1170-1174.

- [16] 郝寅雷, 赵文兴, 翁志成. 新型反射镜材料——碳化硅[J]. 宇航材料工艺, 2001(4): 11-14.

- [17] 付艳艳, 宋月清, 惠松骁. 航空用钛合金的研究与应用进展[J]. 稀有金属, 2006, **30**(6): 850-856.

- [18] 吴凡. 红外成像光学系统无热化设计[J]. 光电技术应用, 2005, **20**(5): 4-29.

- [19] 余怀之. 红外光学材料[M]. 北京: 国防工业出版社, 2007.

- [20] 张舸, 赵文兴. 轻型反射镜镜体结构参数的分析[J]. 光学精密工程, 2006, **14**(1): 49-53.

(上接第 201 页)

- [35] Driggers R G, Vollmerhausen R, Reynolds J P, et al. Infrared detector size: how low should you go?[J]. *Optical Engineering*, 2012, **51**(6): 063202.

- [36] Sofradir shows the future in infrared detection[EB/OL]. 2012-04-23[2013-03-11]. [http://www.sofradir.com/pure-infrared/fr/35/news\\_0\\_2.html](http://www.sofradir.com/pure-infrared/fr/35/news_0_2.html)

- [37] Еремчук А И, Хромов С С, Зайцев А А. Интегральные схемы мультиплексоров современных матричных фотоприемных устройств[J]. *ПРИКЛАДНАЯ ФИЗИКА*, 2011(3): 91-94.

- [38] Mandl W J. Focal plane analog-to-digital conversion development[C] //Proc. of SPIE, 1995, **2474**: 63-71.

- [39] Kang S, Woo D H, Lee H C. Infrared focal plane array readout integrated circuit with on-chip 14 b A/D converter[C] //Proc. of SPIE. 2004, **5234**: 287-295.

- [40] Lu W, Ding R, Liu X, et al. 128×128 dual-color ROIC with electrical crosstalk resistant design[C] //Proc. of SPIE, 2010, **7658**: 7658Z.

- [41] Yazici M, Kayahan H, Ceylan O, et al. Design of a ROIC for scanning type HgCdTe LWIR focal plane arrays[C] //Proc. of SPIE, 2010, **7660**: 76603X.

- [42] Guellec F, Villard P, Rothan F, et al. Sigma-delta column-wise A/D conversion for cooled ROIC[C] //Proc. of SPIE, 2007, **6542**: 65423N.

- [43] Sizov F F, Reva V P, Derkach Y P, et al. Composite readouts with TDI and dead elements deselection[C] //Proc. of SPIE, 2003, **5074**: 911-917.

- [44] Hairston A, Stobie J, Tinkler R. Advanced readout integrated circuit signal processing[C] //Proc. of SPIE, 2006, **6206**: 62062Z.

- [45] Candy J C, Temes G C. A tutorial discussion of the oversampling method for A/D and D/A conversion[J]. *Proc. IEEE Int. Symp. Circuits and Systems*, 1990, **2**: 910-917.

- [46] B. Fowler, A. E. Gamal, D. Yang. Techniques for pixel level analog to digital conversion[C] //Proc. of SPIE, 1998, **3360**: 2-12.