## 〈材料与器件〉

# 77 K 低温下 MOSFET 非固有电容参数提取研究

胡彦博, 李 煜, 白丕绩, 李 敏, 刘会平, 李所英

(昆明物理研究所, 云南 昆明 650223)

**摘要:** 77 K 低温参数是制冷型碲镉汞红外焦平面探测器读出电路设计与精确仿真的关键点之一。通过研究 MOSFET 非固有电容的特性, 并基于 BSIM3 通用模型对电容的描述, 在 77 K 低温下进行测试提取, 得到了相关的模型参数。嵌入 SPICE 软件仿真对比, 证明了参数的准确性。

**关键词:** 77 K 低温, MOSFET, 非固有电容, 参数提取

中图分类号: TN215 文献标识码: A 文章编号: 1001-8891(2013)01-0009-07

## Parameter Extraction of Extrinsic Capacitance of MOSFET at 77 K Cryogenic Temperature

HU Yan-bo, LI Yu, BAI Pi-ji, LI Min, LIU Hui-ping, LI Suo-yin

(Kunming Institute of Physics, Kunming 650223, China)

**Abstract:** Cryogenic parameter in 77K is a key point of cooled MCT infrared detector readout IC design. This paper is a research of characteristic of extrinsic capacitance in MOSFET. Based on the description of capacitance in BSIM3 model, the parameters are measured and extracted at cryogenic temperature. And the parameters are proved accurate by simulate in SPICE.

**Key words:** 77K cryogenic, MOSFET, extrinsic capacitance, parameter extraction

## 0 引言

在制冷型红外焦平面探测器组件中, 读出电路随焦平面工作于 77 K 低温下, 其工作特性和参数与常温下有较大差异。精确的低温模型是红外焦平面探测器 CMOS 读出电路设计的关键要素, 因此提取 77 K 低温条件下 MOSFET 的非固有电容相关参数尤为重要。非固有电容是指除了栅与沟道的 MIS 结构以外的所有电容。在电路设计中, 由于密勒效应的影响, 运算放大器的寄生电容会因为跨导影响放大<sup>[1]</sup>。在相关双采样系统中 MOSFET 开关管的非固有电容会影响开关速率与噪声<sup>[2]</sup>。CMOS 场效应管的非固有电容是低温读出电路设计的核心参数之一, 准确地提取相关寄生电容值, 并针对电路仿真的相关模型进行优化, 是精确控制读出电路内部各级运放工作的零点与极点的先决条件。

## 1 理论分析

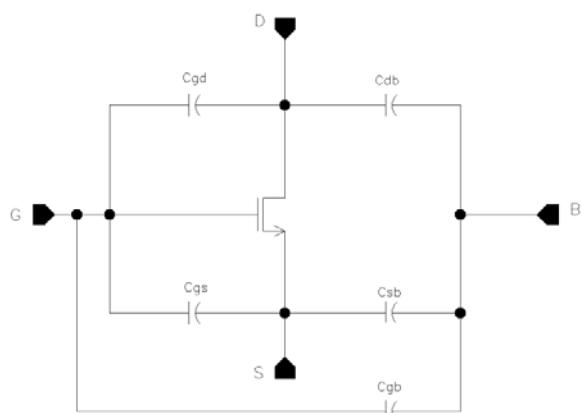

理想 MOSFET 的电容被认为存在于其 4 个端口

之间, 其结构示意如图 1 所示。

图 1 MOSFET 电容理论分布

Fig.1 Theoretical capacitance of MOSFET

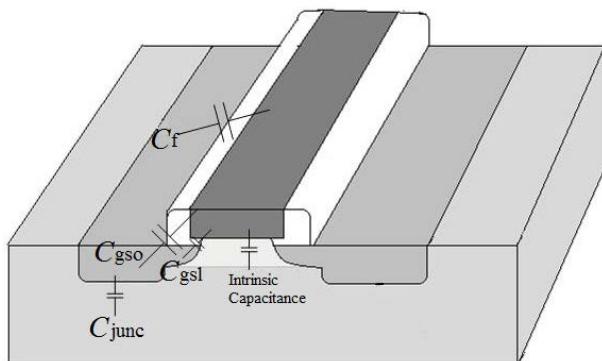

实际的物理器件电容值由各端点的物理结构决定。如图 2 所示, 基于 MOSFET 结构的源、漏极对称性, 图 2 只标注了源端注入区与栅极间的电容, 漏端与源端的电容构成实际是相同的。其中各电容

示意均与沟道宽度成正比,因此参数实际上是单位沟道宽度的电容值(单位为F/m)。除了多晶硅栅与沟道之间的氧化层电容以及衬底与耗尽层之间的电容外,其与源、漏区域以及外部边缘,以及注入区与周围接触面均有寄生电容存在<sup>[3]</sup>。

Fig.2 Different parts of the capacitance of MOSFET

图2中,  $C_f$  表示多晶硅栅外部边缘同源、漏形成的寄生电容, 该电容值是栅氧侧墙介电常数与栅氧化层厚度的函数;  $C_{gso}$  表示多晶硅栅与源端注入区的重掺杂区域重叠的部分形成的电容;  $C_{gsl}$  表示多晶硅栅与源端注入区的轻掺杂区域重叠的部分形成的电容。轻掺杂源、漏区域结构又称 LDD 结构, 其引入的作用是降低沟道与源、漏区域结合部分的电荷浓度梯度, 使该部分的场强显著降低, 抑制热载流子效应对栅氧化层的侵害<sup>[4]</sup>。LDD 区的引入给栅极与注入区带来了更大的叠层电容。通过查询相关模型文件可知, 使用 LDD 工艺与传统工艺生产的两种不同工艺制造的 MOSFET 器件  $C_{gsl}$  值差距巨大。 $C_{junc}$  表示源、漏与衬底产生的电容, 该电容值是衬底电压、源漏面积与周长相关的函数。

因此从 MOSFET 器件角度观察, 其非固有电容分为 2 个部分:

①注入区与衬底间的电容;

②栅与源、漏注入区之间的叠层电容与边缘寄生电容。

选用 Global Foundries 代工的 0.35 μm 2P3M 电路工艺设计测试芯片, 制作不同尺寸的 MOSFET。使用 Agilent 4294A 阻抗分析仪测试 300 K 与 77 K 下的器件特性:

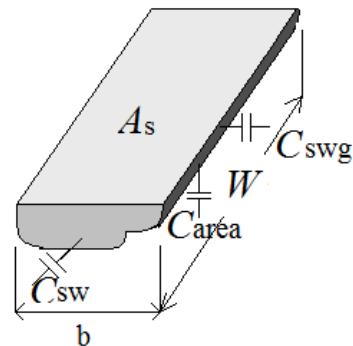

1) 源、漏注入区与衬底的寄生电容  $C_{junc}$  的结构分析:

$C_{junc}$  的具体组成结构如图 3 所示。

对各区域电容的定义与标识如下:

$C_{area}$  表示注入区底面与衬底的纵向接触电容,

其为注入区面积相关的值, 单位为 F/m<sup>2</sup>;

$C_{sw}$  表示注入区外围侧墙与衬底的接触电阻, 其为注入区周长相关的值, 单位为 F/m;

$C_{swg}$  表示注入区边缘有栅极覆盖的侧墙产生的电容, 单位也为 F/m。

Fig.3 Source region capacitance parts

试验中测量得到的值都是有特定尺寸的电容值, 实际电路仿真中需要使用的是单位面积或单位长度侧墙围线的电容值(由于工艺中源、漏的对称性, 实际上各面积、参数、电容值变量中的漏端和源端标识符  $d$ 、 $s$  都是可以互换的):

$$C_{area} = A_s \cdot C_{jbs} \quad (1)$$

$$C_{sw} = (P_s - W) \cdot C_{jbsw} \quad (2)$$

$$C_{swg} = W \cdot C_{jbswg} \quad (3)$$

$A_s$  (Area of Source) 为版图上源端注入区的面积;  $P_s$  (Perimeter of Source) 为版图上源端注入区的周长;  $W$  为多晶硅栅的长度;  $C_{jbs}$  为单位面积的注入区与衬底接触电容;  $C_{jbsw}$  为单位长度注入区侧墙与衬底接触电容;  $C_{jbswg}$  为单位长度注入区侧墙有栅极覆盖的一侧与衬底的接触电容。

BSIM3 模型中对  $C_{jbs}$ 、 $C_{jbsw}$ 、 $C_{jbswg}$  的拟合方式如下:

$$C_{jbs} = \begin{cases} C_j \left(1 - \frac{V_{bs}}{P_b}\right)^{-M_j}, & V_{bs} < 0 \\ C_j \left(1 + M_j \frac{V_{bs}}{P_b}\right), & V_{bs} \geq 0 \end{cases} \quad (4)$$

$$C_{jbsw} = \begin{cases} C_{jsw} \left(1 - \frac{V_{bs}}{P_{bsw}}\right)^{-M_{jsw}}, & V_{bs} < 0 \\ C_{jsw} \left(1 + M_{jsw} \frac{V_{bs}}{P_{bsw}}\right), & V_{bs} \geq 0 \end{cases} \quad (5)$$

$$C_{jbswg} = \begin{cases} C_{jswg} \left(1 - \frac{V_{bs}}{P_{bswg}}\right)^{-M_{jswg}}, & V_{bs} < 0 \\ C_{jswg} \left(1 + M_{jswg} \frac{V_{bs}}{P_{bswg}}\right), & V_{bs} \geq 0 \end{cases} \quad (6)$$

$P_b$ 、 $P_{bsw}$  以及  $P_{bswg}$  为源、漏与注入区相关内建电势差参数,  $M_j$ 、 $M_{jsw}$  和  $M_{jswg}$  为各部分电容相关系数。

## 2) 棚与源漏寄生电容参数的结构分析:

如图 2 所示, 棚与源漏注入区一共有三处寄生电容: 棚与源、漏重掺杂区形成的电容  $C_{gso}$ 、 $C_{gdo}$ ; 棚与源、漏轻掺杂区 LDD 结构形成的电容  $C_{gsl}$ 、 $C_{gdl}$ 。上述两处电容均由棚极与源、漏区域交叠部分形成, 统称叠层电容。此外棚与源、漏注入区外层的边缘电容因为无法在测试中通过改变测试条件加以区分, 在测量上述电容时也会被同时测量到。

$C_f$  形成于注入区与棚极外延。一般说来其在测试图形上若无法与棚和注入区叠层电容区分开来, 则使用以下经验公式进行计算:

$$C_f = \frac{2\epsilon_{SiO_2}}{\pi} \ln \left(1 + \frac{4 \times 10^7}{T_{ox}}\right) \quad (7)$$

式中:  $\epsilon_{SiO_2}$  为当前温度下的棚氧化层介电常数;  $T_{ox}$  为棚氧化层厚度。

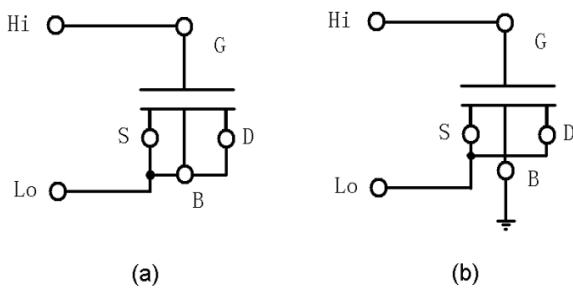

棚极与源、漏叠层的电容则需要实际测试求得。测试选用 55 叉指  $100 \mu m \times 0.8 \mu m$  NMOS 和 70 叉指  $100 \mu m \times 0.4 \mu m$  NMOS 测量棚与并联源漏间的叠层电容以及棚与并联的源漏、衬底间的总电容, 分别表示为  $C_{g\_ds}$  和  $C_{g\_bds}$ 。测试通过如图 4 所示的方式连接, 其中 Hi 和 Lo 分别为阻抗分析仪的高电位接入点和低点位接入点:

图 4 测试电容的连接方式: (a) 棚与源、漏、衬底电容;

(b) 棚与源、漏电容

Fig.4 Connection of capacitance sample: (a) Between gate and source/drain/bulk, (b) Between gate and source/drain

图 4 中的连接方法默认了棚与漏制造工艺是对称的, 即  $C_{gso}$  和  $C_{gsl}$  以及  $C_{gdo}$  和  $C_{gdl}$  是相等的。通过上述连接并施加扫描电压即可测得相应情况下的

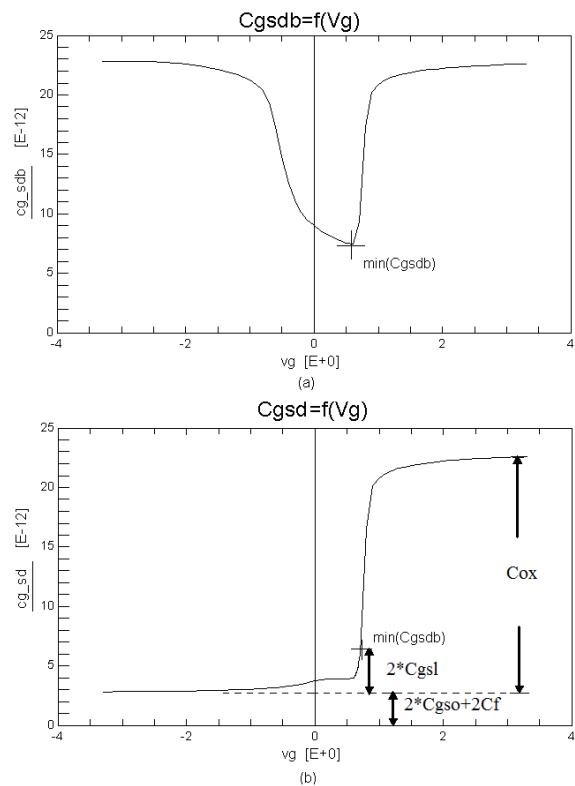

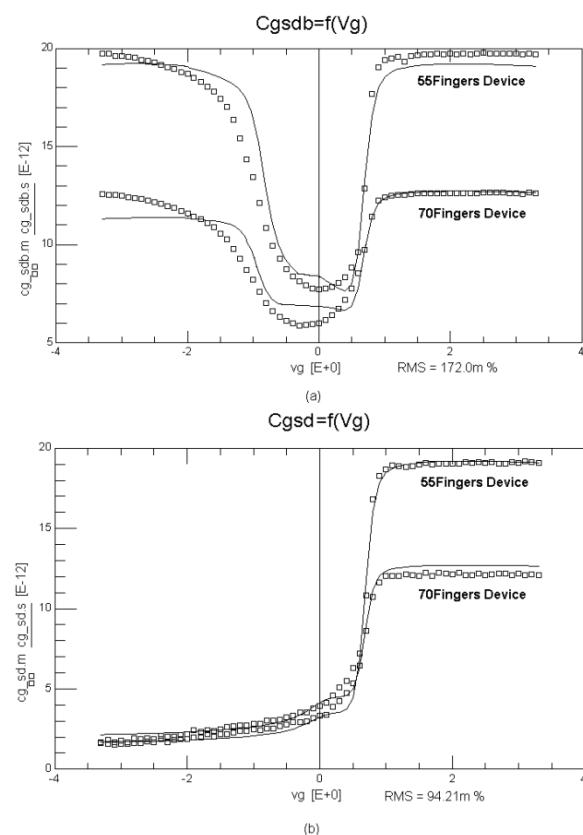

电容值。其  $C-V$  对应的坐标曲线在图 5 中展示。

如图 5(a), 通过测试上述结构可以求得棚与源、漏、衬底电容  $C_{g\_sdb}$  的最小值。该值代表了棚与沟道间偏压不足以使半导体表面出现反型, 即沟道空间电荷呈耗尽状态时的值。此时为器件提供电容值的即为棚与源、漏区域的总寄生电容值。为棚与源、漏的叠层电容与边缘电容共同贡献。

图 5 电容测试曲线示意图: (a) 棚与源、漏、衬底电容;

(b) 棚与源、漏电容

Fig.5 Sketch of capacitance test curve: (a) between gate and source/drain/bulk, (b) between gate and source/drain

在测试过程中,  $C_{gso}$  与  $C_f$  的值是不可区分的。但是从 MOSFET 器件结构上观察,  $C_{gso}$  来自于制造过程中多晶硅淀积以后注入区形成时造成的棚长失配, 即多晶硅棚与源、漏高浓度注入区在垂直于晶圆平面的方向上有重叠 (这也是为了保证棚压与沟道连续性的工艺措施), 因此这一电容值与棚长失配相关。棚长失配是代工厂技术因素影响的一个固定值, 与温度以及施加棚压无关。BSIM3v3 模型中该失配值参数定义为 LINT。 $C_{gsl}$  与  $C_{gdl}$  的计算如图 5 所示, 为棚与源、漏、衬底电容测量最小值与棚与源、漏电容测量最小值之差。棚与源、漏、衬底电容测量最小值的测量结果在图 5(a)中可以得到。 $C_{gso}$  的值可通过棚长失配度求得。如图 5(b), 定义沟道单位宽度的总电容值为  $C_{ox}$ , 则单位棚宽的重掺杂

层叠电容可由下式求得：

$$C_{gso} = LINT \times C_{ox} - C_{gsl} \quad (8)$$

这样，通过图5(b)中电容最小值以及计算得到的 $C_{gso}$ 值即可求得 $C_f$ 值。

## 2 测试与提取

### 2.1 注入区电容测试与提取

在代工厂提供的通用常温模型下，没有 $C_{jswg}$ 参数，仿真时将其等同于 $C_{jsw}$ 值，本实验将通过测试研究该参数仿真时是否能够与 $C_{jsw}$ 合并。

测试 $C_{junc}$ 与其他电容需要不同的结构：实验选用三种不同的器件结构来进行测试：

①注入区底面接触电容测试器件 $C_1$ : 100 μm × 100 μm 的大面积源/漏注入与衬底形成的电容，用于测量大面积注入区与衬底的电容和二极管特性。因为其正方形结构在四边形中能够达到最大的注入区面积-周长比，故测试结果中 $C_{area}$ 的值体现的最为明显，而侧墙电容 $C_{sw}$ 影响能够降到最低；；

②注入区侧墙电容测试器件 $C_2$ : 56 叉指 100 μm × 1 μm (大宽长比) 的源/漏注入区与衬底形成的电容，用于测量叉指形注入区与衬底的电容和二极管特性。因为其具有较大的宽度，故注入区面积-周长比能够尽可能大，将侧墙电容 $C_{sw}$ 的值体现的更加明显。

③有栅接触边影响的注入区侧墙电容测试器件 $C_3$ : 含 55 根浮置多晶硅栅的 56 叉指 100 μm × 1 μm 的源/漏注入区与衬底形成的电容，用于测量含多晶硅栅情况下的叉指形注入区与衬底的电容和二极管特性。同 $C_2$ 测试器件相类似，较大的栅与注入区接触面使得栅极影响区域侧墙电容 $C_{swg}$ 的值体现得更明显，此外更宽的多晶硅栅可以尽可能减小芯片制造过程中造成的栅极宽度失配影响。

三种测试结构的总电容值如下：

$$\begin{cases} C_1 = 10000C_{jbs} + 400C_{jbsw} \\ C_2 = 5600C_{jbs} + 11312C_{jbsw} \\ C_3 = 5600C_{jbs} + 112C_{jbsw} + 11200C_{jbswg} \end{cases}$$

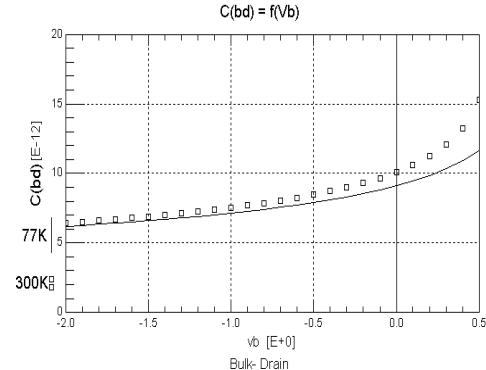

测试将器件安置在 Lakeshore TTP4 低温探针台中并通入液氮制冷至 77 K，并用探针将测试端口引出。使用阻抗分析仪高电位端接注入区，低点位端接衬底，对 P 衬底上进行 N 注入的器件施加 -3.3 ~ 0.5 V 的扫描电压，得到电容特性曲线。如图 6 是器件 $C_1$ 在 300 K 与 77 K 下测试得到的 C-V 特性曲线。

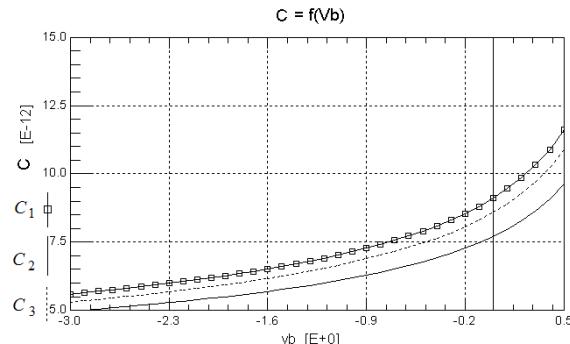

实际的电路设计中 N 型 MOSFET 衬底电压往往为 0 或负值，故 $V_{bs} = -3 ~ 0$  V 区域是主要的研究对象。对设计的三个测试器件在 77 K 条件下进行实际测试，得到的测试数据如图 7 所示。为了使提取到的测试数据更完全，选取衬底电压范围为 -3 ~ 0.5 V。

由图 7 对照公式(4)、(5)、(6)可得： $C_j$ 、 $C_{jsw}$ 、 $C_{jswg}$ 的具体值可由 $V_{bs} = 0$  点测出：

$$\begin{cases} 10000C_{jbs} + 400C_{jbsw} = 9.108 \text{ pF} \\ 5600C_{jbs} + 11312C_{jbsw} = 7.702 \text{ pF} \\ 5600C_{jbs} + 112C_{jbsw} + 11200C_{jbswg} = 8.583 \text{ pF} \end{cases}$$

$$\begin{cases} C_j = 0.9108 \text{ mF/m}^2 \\ C_{jsw} = 2.346 \text{ pF/m} \\ C_{jswg} = 5.520 \text{ pF/m} \end{cases}$$

这些值相对于 300 K 下的情况都有不同程度的减小，这也印证了图 6 反映出的测试结果。将 $C_1$ 的测试点坐标值输入 SigmaPlot 软件线性回归求得 $M_j = 0.2701$ ， $P_b = 0.6119$ 。将上述值代入 $C_2$ 器件曲线可求得 $C_{jbsw}$ 随 $V_{bs}$ 的变化曲线。使用同样的回归方式可得到以上相关参数值。

图 6  $C_1$  器件在 300 K 与 77 K 下电容测量值对比

Fig.6 Capacitance measurement results of  $C_1$  at 300 K and 77 K

图 7 77 K 器件下  $C_1$ 、 $C_2$  以及  $C_3$  测量值

Fig.7 Measurement results of  $C_1$ ,  $C_2$  and  $C_3$  devices at 77 K

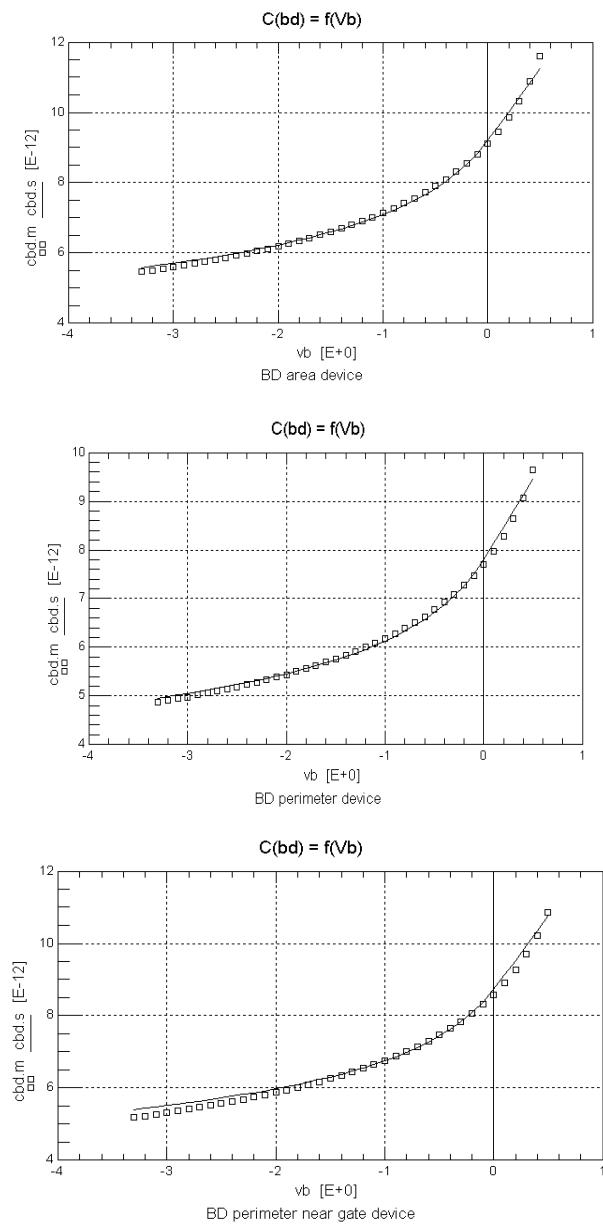

图8为使用SPICE仿真得到的电容特性曲线与测量值对比,其中方块为77 K下实际测量值,实线为低温电容参数代入仿真得到的所得的值。自上至下依次展示了源漏注入区底面与衬底接触面的电容、源漏注入区侧墙与衬底接触=的电容以及栅接触边影响的注入区侧墙与衬底接触的电容:

图8 源、漏与衬底接触电容测量与仿真图形对比

Fig.8 Simulation and measurement of capacitance between source/drain and bulk

由图8可见提取的参数值在SPICE仿真中能较好地同测量值吻合。

## 2.2 注入区与栅极叠层电容测试与提取

测试的器件结构同样选用大栅宽的55叉指器件,栅极长度为0.8 μm,以尽量减小沟道电容与寄生电容比率,使寄生电容更容易被测试;栅极宽度

为100 μm,以尽量减小栅宽失配造成的数据误差,乘以叉指栅宽一共是5500 μm,以尽量放大寄生电容值。作为对比测试选用70叉指栅极长度为0.4 μm、宽度为100 μm的器件,多次测量使用最小二乘法拟合所求参数值。

在77 K下得到的测试与仿真结果如图9,方块为测量值,实线为仿真值。其中施加正向栅压时电容值较大的为55叉指器件(因为其栅总面积更大),电容值较小的为70叉指器件:

图9 电容仿真曲线对照图: (a) 栅与源、漏、衬底电容; (b) 栅与源、漏电容

Fig.9 Curve of capacitance measurement and simulation: (a) between gate and source/drain/bulk, (b) between gate and source/drain

如图9可见,对于栅与源、漏间电容的仿真具有较高的精确度,说明提取计算得到的MOSFET各部分寄生电容在低温下的值是准确的。在运算放大器设计中可以将上述计算方法提取到的参数投入设计实用。

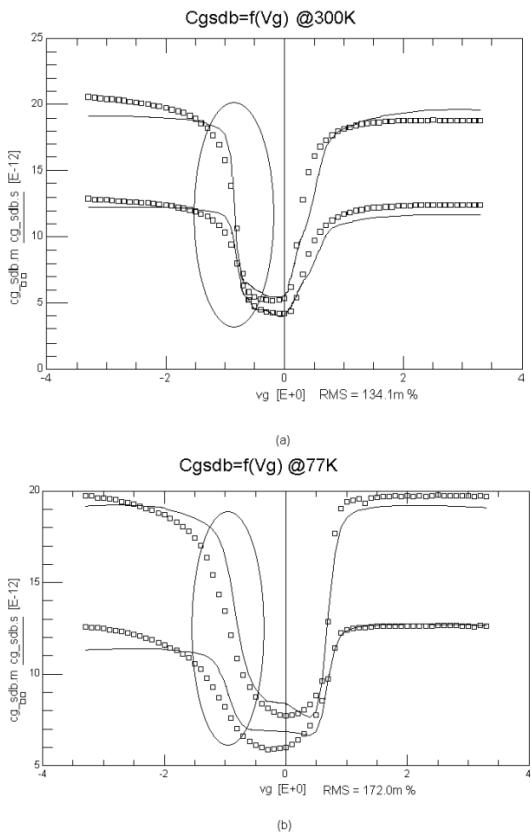

但是在栅与源、漏、衬底电容仿真上,施加负的栅压时出现了较大的失配,这种现象与MIS结构半导体电容本身在低温下的性质有关<sup>[5-6]</sup>:77 K下沟道处于低温弱电离区,本征载流子浓度n<sub>i</sub>相比常温下大幅降低,导带中的电子全部由电离施主杂质提

供,载流子的产生与复合量被限制在较低水平,这样在低频测试的情况下,C-V特性由低频型向高频型过渡,具体体现在 $V_g$ 在0~−2 V区间上电容值的实际变化幅度低于仿真结果,若要得到更精确的仿真结果,须要设计其他实验对载流子在低温下的复合与产生进行相关实验。实验采用相同测试管与测试设备在常温下进行上述测试,如图10(a),得到的电容变化率曲线符合仿真得到的相应曲线,而图10(b)则有一定失配。

图10 棚与源、漏、衬底电容仿真曲线对照图: (a) 温度为300 K; (b) 温度为77 K

Fig.10 Curve of capacitance simulation between gate and source/drain/bulk: (a) at 300 K, (b) at 77 K

### 2.3 数据整理与仿真

以N型MOSFET为实验对象,通过仿真对比基本达到了77 K下MOSFET寄生电容的精确提取。

提取到的低温参数如表1所示,300 K时的数据由代工厂提供。其中由于代工厂BSIM版本关系没有提供注入区贴近栅端单位长度电容值。通过将代工厂数据代入SPICE仿真器与常温提取得到的均方根误差也在极小的范围内,证明实验操作与器件结构设计是正确的。

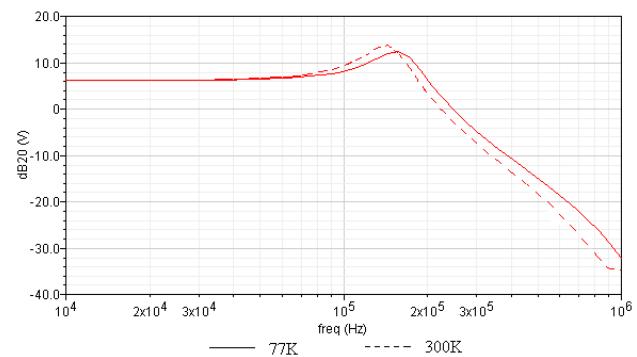

将适用于常温仿真的模型文件的电容部分参数值修改为77 K低温下提取到的参数值,对一个二级

运放进行频率仿真,以观察其输出结果变化。

图11为对二级运放的频率特性仿真结果,可见电容随温度的变化对运放极点产生了影响,较小的寄生电容使得零点向高频段偏移。这说明低温电容参数是读出电路设计的重要因素之一。

表1 提取得到的电容参数值

Table 1 Extraction results of capacitance parameters

| 模型参数       | 单位 <sup>*</sup> | 77 K                       | RMS         | 300 K                      | RMS         |

|------------|-----------------|----------------------------|-------------|----------------------------|-------------|

| $C_j$      | $F/m^2$         | 0.9108<br>$\times 10^{-3}$ | $\approx 0$ | $\times 10^{-3}$           | $\approx 0$ |

| $M_j$      | —               | 0.2701                     |             | 0.3600                     |             |

| $P_b$      | V               | 0.6119                     |             | 0.7630                     |             |

| $C_{jsw}$  | $F/m$           | 234.6<br>$\times 10^{-12}$ |             | 380.0<br>$\times 10^{-12}$ |             |

| $M_{jsw}$  | —               | 0.1931                     | 1.195%      | 0.2693                     | 1.881%      |

| $P_{bsw}$  | V               | 0.4504                     |             | 0.5920                     |             |

| $C_{jswg}$ | $F/m$           | 332.0<br>$\times 10^{-12}$ |             | —                          |             |

| $M_{jswg}$ | —               | 0.2109                     | 2.753%      | —                          | —           |

| $P_{bswg}$ | V               | 0.4028                     |             | —                          |             |

| $C_{gsl}$  | $F/m$           | 215.0<br>$\times 10^{-12}$ |             | 220.0<br>$\times 10^{-12}$ |             |

| $C_{gso}$  | $F/m$           | 82.07<br>$\times 10^{-12}$ | 0.172%      | 105.0<br>$\times 10^{-12}$ | 0.134%      |

| LINT       | m               | 41.20<br>$\times 10^{-9}$  |             | 41.20<br>$\times 10^{-9}$  |             |

\*由于 $C_j$ 是注入区底面单位面积的电容值,因此单位为 $F/m^2$ ;同种工艺下注入区的深度是相同的,因此侧墙电容的变量为注入区周长, $C_{jsw}$ 和 $C_{jswg}$ 是单位长度的电容值,单位为 $F/m$ 。

图11 77 K与300 K下二级运放仿真频率特性曲线对比

Fig.11 Curves of frequency characteristic of two stages amplifier at 77 K and 300 K

### 3 结论

1) 77 K 下 MOSFET 的各部分寄生电容值均比 300 K 时测量得到的小, 这是由于低温下半导体器件各部分载流子浓度以及材料介电常数随温度变化决定的;

2) 注入区与衬底的纵向接触电容在有无栅接触情况下有显著差异,  $C_{jswg}$  与  $C_{jsw}$  不可等同;

3) 由于 LDD 工艺, 注入区与栅极间具有较大的叠层电容, 在运放设计时需要进行考虑;

精确仿真制冷型碲镉汞红外焦平面探测器读出电路还需很多其他部分低温参数, 例如要精确地仿真施加负栅压的情况, 还需结合低温下载流子的产生与复合进行进一步分析; 从 77 K 低温下运算放大器仿真可看出, 读出电路工作的零极点会受温度产生变化, 其原因之一是非固有电容的变化。今后将结合 MOSFET 其他方面参数的提取, 进行更进一步的仿真, 得到更精确的结果。

### 参考文献:

- [1] 拉扎维. 模拟 CMOS 集成电路设计[M]. 陈贵灿, 程军, 张瑞智, 等译. 西安: 西安交通大学出版社, 2003: 142-145.

- [2] Martin Patrick, Guellec Fabrice. MOSFET Modeling for Simulation, Design and Optimization of Infrared CMOS Image Sensors Working at Cryogenic Temperature[C]//MIXDES 2011, 18th International Conference "Mixed Design of Integrated Circuits and Systems", 2011: 16-18.

- [3] Yeh Wen-Kuan, Ku Chao-Ching, Chen Shuo-Mao, et al. Effect of Extrinsic Impedance and Parasitic Capacitance on Figure of Merit of RF MOSFET[J]. IEEE transactions on electron devices, 2005, **52**(9): 2054-2060.

- [4] 甘学温, 黄如, 刘晓彦, 等. 纳米 CMOS 器件[M]. 北京: 科学出版社, 2004.

- [5] 刘恩科, 朱秉升, 罗晋生, 等. 半导体物理[M]·7 版. 北京: 电子工业出版社, 2008: 252-253.

- [6] Akturk Akin, Allnutt Jeffrey, Dilli Zeynep, et al. Device Modeling at Cryogenic Temperatures: Effects of Incomplete Ionization[J]. IEEE transactions on electron devices, 2007, **54**(11): 2984-2990.

## 关于《红外技术》期刊采编系统正式运行的启事

《红外技术》的网站 (<http://hwjs.nvir.cn>) 已于 2012 年 11 月开通, 期刊采编系统也正式启用。该系统将为作者、审稿专家、读者和编辑之间搭建一个便捷的交流平台。作者今后可以通过这个网站在线投稿并查询审稿进度。审稿专家也可以通过网站进行在线审稿。

由于本刊采编系统启用不久, 可能会有不尽完善之处, 欢迎广大作者、读者以及审稿专家在使用过程中提出宝贵意见和建议, 编辑部将会及时进行调整。

《红外技术》编辑部

2013 年 1 月