# 短波 320×256 抗辐射加固读出电路设计

梁 艳, 李 煜, 王 博, 白丕绩, 李 敏, 陈 娥

(昆明物理研究所, 云南 昆明 650223)

**摘要:** 设计了一款采用 CMOS 工艺的短波 320×256 抗辐射加固读出电路, 分析了 CMOS 工艺抗辐射的特点, 重点介绍了模拟通路、偏压产生电路和数字电路的加固设计方法, 采用了双环保护结构、对 NMOS 管使用环形栅和冗余设计等措施。该设计电路经过流片, 测试结果表明该抗辐射加固设计方法有效可行。

**关键词:** CMOS; 读出电路; 抗辐射加固

中图分类号: TN215

文献标识码: A

文章编号: 1001-8891(2012)12-0705-05

## Radiation-Hardened Design for Short Wave 320×256 Read-Out Integrated Circuit

LIANG Yan, LI Yu, WANG Bo, BAI Pi-ji, LI Min, CHEN Xiao

(Kunming Institute of Physics, Kunming 650023, China)

**Abstract:** This paper presents a 320×256 short wave radiation hardened Read-Out Integrated Circuit using CMOS process, analyses the characteristic of CMOS process. And methods on reliability design for analog path, voltage bias generating circuit and digital circuit are emphatically introduced. Measures as guard banding, edgeless NMOS transistors, redundancy design are taken. The circuit has been made and the feasibility of the design for radiation hardened was confirmed by the test results.

**Key words:** CMOS, ROIC, radiation hardened

## 0 引言

随着超大规模集成电路的快速发展, 红外焦平面阵列 (IRFPA) 在航天航空领域及空间科学探测中得到广泛的应用。很多卫星、飞机、导弹等军用或民用设施上都配有红外焦平面阵列, 它主要由探测器阵列与读出电路构成。探测器阵列的作用是采集光信号; 读出电路用于处理并输出探测器阵列所采集到的光信号, 它参与了光信号的传输过程, 其性能好坏直接影响红外焦平面阵列的性能指标。由于空间辐射环境中存在大量 X 射线、 $\gamma$ 射线、 $\alpha$ 粒子、高能质子、中子等高能粒子, 当红外焦平面阵列在空间辐射等恶劣环境下使用时, 这些射线和带电粒子与读出集成电路相作用, 容易造成读出电路信号处理出错、传输失真及信号衰减或跳变等一系列问题, 使电路性能参数严重退化甚至失效, 从而导致红外焦平面阵列无法正常工作。因此对读出电路进行抗辐射加固, 提高红外焦平面阵列在空间辐射环

境中的可靠性, 对空间技术的发展具有非常重要的意义。

## 1 抗辐射加固设计

辐射对集成电路的影响可分为位移效应和电离辐射效应。对 CMOS 电路影响较大的是电离辐射效应, 电离辐射效应主要包括总剂量辐射效应 (TDI, total ionizing dose)、单粒子效应及剂量率辐射效应。

TDI 效应会形成栅氧空穴捕获 (oxide charge trapping) 与界面捕获 (interface charge trapping)。从而出现 NMOS 管阈值电压下降, 容易导通, 漏电流增加; PMOS 管阈值电压变得更负(绝对值升高), 难以导通, 驱动能力下降等现象<sup>[1]</sup>。

辐射环境中的存在大量的 $\gamma$ 粒子、 $\alpha$ 粒子、中子、高能质子等粒子, 这些粒子在读出电路中会引起电路的瞬时扰动, 这种效应称为单粒子效应。单粒子效应主要包括单粒子翻转和单粒子闩锁。

在核辐射环境下, 会在短时间内淀积大剂量的

收稿日期: 2012-10-25.

作者简介: 梁艳 (1982-), 女, 本科, 助理工程师, 主要研究方向为读出电路设计。

基金项目: 国家重大专项项目。

能量,产生剂量率效应。剂量率效应对CMOS器件的主要影响是在内部PN结中形成瞬时光电流。

读出电路的功能是对探测器采集到的光信号进行处理、保持和输出。 $320 \times 256$ 抗辐射加固CMOS读出电路的功能结构主要包括单元阵列、行/列地址译码、时序产生电路、偏置电压产生电路和输出运放电路。设计时需要根据辐射效应及电路功能,有针对性地采取加固措施,才能有效提高读出电路的抗辐射能力。

## 1.1 加工工艺

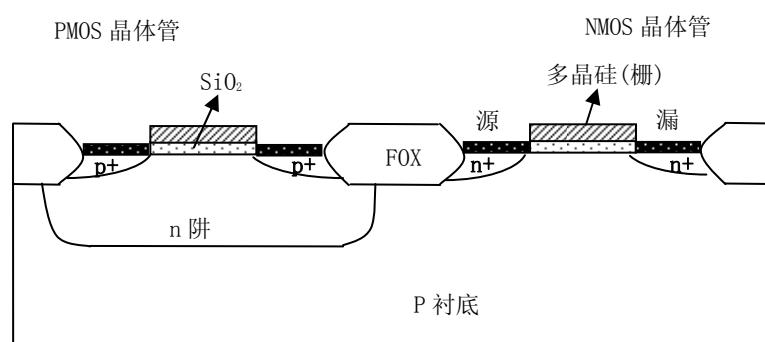

本文读出电路的设计基于CMOS(Complementary Metal Oxide Semiconductor)技术。目前,CMOS技术已成为VLSI(超大规模集成电路)数字和混合信号设计的主导技术。图1为采用n阱p衬底CMOS工艺制作的mos晶体管结构示意图。CMOS工艺用厚场氧化物(FOX)来隔离器件。正常工作时,源漏区和沟道所构成的有源部分与衬底之间处于反偏状态,从而使整个器件与衬底之间在电学上是完全隔离的。其基本工作原理是通过改变栅/源电压来控制沟道导电能力,从而控制漏极电流的大小。

CMOS工艺制作的集成电路具有低功耗、高集成度、温度稳定性好、工艺成熟、成本较低等优点。随着CMOS集成电路发展至深亚微米时代,可以不

用像过去那样从特殊的抗辐射工艺线获得抗辐射集成电路,而采用CMOS工艺,并对电路采取加固措施来得到抗辐射性能较好的集成电路。CMOS器件是多子器件,具有很好的抗中子辐射能力,中子一般可达到 $10^{14} \text{ cm}^{-2}$ 以上。但是由于CMOS器件固有的pnnp四层结构,构成了寄生的可控硅结构,从而易发生单粒子闩锁效应<sup>[2]</sup>。CMOS器件采用反偏PN结进行隔离,CMOS晶体管的阈值电压对辐射很敏感,因为有源区的源漏和衬底是连通的,在辐照下会产生大量的电子空穴对,从而影响器件的正常工作,严重时会导致电路的失效。所以需要对CMOS读出电路进行抗总剂量、抗剂量率和抗单粒子辐射加固设计。

## 1.2 关键模块辐射加固设计

### 1.2.1 模拟电路设计

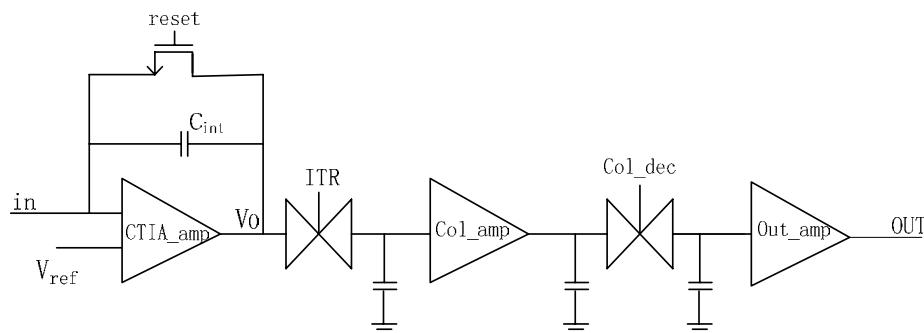

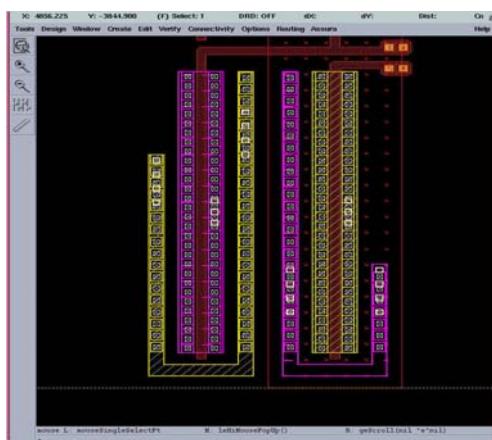

在模拟电路中,运算放大器不仅要处理前一级送来的信号,还要在不损害放大器性能的条件下驱动后续信号处理电路,受辐射影响会使运算放大器工作点漂移,影响运算放大器正常工作,从而影响读出电路的性能。短波 $320 \times 256$ 读出电路的模拟通路如图2所示,运放电路包括输入级运放电路、列级运放电路和输出级运放电路。

图1 CMOS工艺制作的晶体管

Fig.1 Transistors using CMOS process

图2 模拟信号通路示意图 Fig.2 The schematic representation of analog signal path

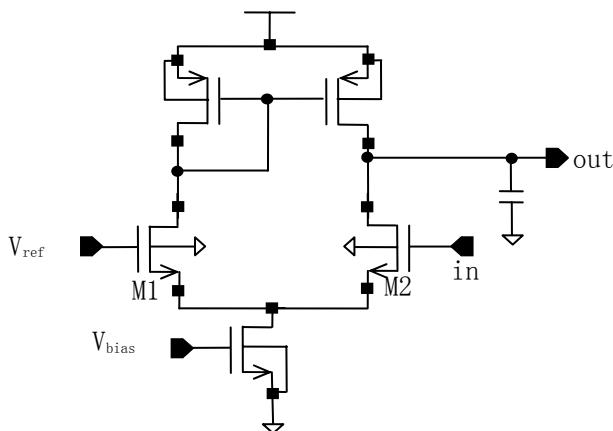

总剂量效应会引起晶体管阈值电压漂移,设计运放电路时,根据 NMOS 管和 PMOS 管阈值电压漂移的不同情况进行仿真,根据仿真结果并结合运放的功耗、增益等条件,调节运放偏置电压与晶体管尺寸,即对辐照后因晶体管参数退化影响整体电参数进行冗余设计<sup>[3]</sup>,提高运放电路的电参数水平。以输入级运放为例,见图 3。

图 3 CTIA 运放示意图

Fig.3 CTIA operational amplifier circuit

CTIA 运放到总剂量辐射影响后, NMOS 晶体管  $M_1$  和  $M_2$  阈值电压变小,更小的电压就可以使  $M_1$  和  $M_2$  导通,从而使输出电压摆幅增大,但是增大的部分引入的信号是非线性的,所以设计时需要减小电压输出摆幅。图 2 中,输入级积分电容左端电压与  $V_{\text{ref}}$  相等,右端近似有  $V_0 = IT/C_{\text{int}} + V_{\text{ref}}$ , (积分时,积分电容放电),其中,  $V_{\text{ref}}$  为积分电容复位参考电压,  $I$  为积分电流,  $T$  为积分时间,  $C_{\text{int}}$  为积分电容。由公式可以看出:  $IT/C_{\text{int}}$  不改变时,增加  $V_{\text{ref}}$  值会使  $V_0$  增大,而  $V_0$  的最大值受电源电压限制,这样就使  $V_0$  的最小值增加,减小了  $V_0$  的变化范围,即减小了电压输出摆幅。因此设计时,适当增加  $V_{\text{ref}}$  的值以达到减小总剂量辐射效应影响的目的。

版图设计时,在运放中使用环形栅和保护环,以阻断辐射感生源/漏极间电流泄漏通道的形成,消除场氧反型漏电效应。从而稳定晶体管阈值电压,减小辐射效应造成的运放工作点漂移,降低电路对单粒子闩锁效应的敏感性,并根据模拟电路中晶体管及电容功能的不同进行分块隔离,减小相互串扰。

模拟电路通过开关管和电容来传输和存储信号,辐射产生的单粒子效应还容易使开关传输管发生逻辑错误,故采用 CMOS 开关代替常用的单管传输,减小开关管受单粒子效应发生逻辑错误的几率。

## 1.2.2 偏压产生电路设计

偏置电压用于调节运算放大器的工作点,由电路内部产生,如果偏置电压受辐射影响发生偏移,会使运算放大器的工作状态发生改变,甚至无法工作。因此,需要采取加固措施来减小偏置电压在辐射环境下的偏移量,使偏置电压产生电路具有一定的稳定性。

要消除 TDI 效应对电路的影响,最有效的方法是改变晶体管的栅结构。本文采用环形栅来消除 TDI 效应对偏压产生电路的影响,不足之处是这种栅结构需要占用较大版图面积。受面积限制,且 PMOS 管不存在边缘寄生晶体管反型的问题,故本文在偏压电路设计时,只对 NMOS 管使用环形栅结构(见图 4),并在 NMOS 管周围增加 P\_SUB 保护环接 GND。由于辐射会造成 PMOS 管驱动能力下降,故设计时,对 PMOS 管的沟道进行适当补偿,平衡 NMOS 管和 PMOS 管的驱动能力。

图 4 NMOS 管环形栅

Fig.4 Edgeless NMOS transistors

## 1.2.3 数字电路设计

随着目前器件特征尺寸的减小,临界电荷越来越小,使单粒子效应发生的几率变高。当等离子体径迹附近存在电势差时,会引起电荷的转移,当电荷转移足够大时,将引起相关单元逻辑状态改变,即逻辑翻转,单粒子翻转主要发生在数字电路、动态存储电路中。

受单粒子翻转效应及剂量率效应影响,数字电路容易发生逻辑错误。本文对数字存储单元采取冗余锁存的办法,即将关键的数字信号存储到不同的地方,当受到辐射影响时,可以通过反馈将受损数据恢复,从而减小数字信号被损坏的几率。但由于冗余锁存需要占用较大版图面积,所以只在部分关键数字电路中使用。

## 1.3 其他加固措施

除了上文提到的加固措施，该款电路中还采用了以下几种措施，以进一步提高电路的抗辐射能力：

1) 增加电流泄漏通道，使因辐射产生的突然增大的电流分流到地，避免产生闩锁，减小剂量率辐射效应和单粒子效应的影响，保护电路功能的正常。

2) 受辐射影响，单粒子闩锁效应在 CMOS 器件中很容易出现。解决办法是在全电路中大量使用保护环：在漏电流沟道上插入一条重掺杂的 P\_SUB 保护环，消除了场氧反型漏电效应，可以阻断 N 阵中的阱接触高电位 VDD 和 P 阵中 N 管的源极电位 VSS 之间形成的漏电沟道，有效的减轻总剂量电离辐射感生的场氧漏电效应；增加 P\_SUB 保护环接 GND，增加 N\_WELL 保护环接 VDD（见图 5）。闩锁效应是 CMOS 电路的固有问题，保护环可以作为

衬底接触区有效减轻单粒子闩锁效应的影响<sup>[4,5]</sup>。

3) 读出电路的最上层增加一层金属层，并将这层金属通过端口直接接到读出电路外面的地，即该层金属的泄漏通道不通过读出电路内部。这样，可以有效减小辐射粒子对读出电路的影响。

4) 版图设计时走线尽量紧凑，减小寄生效应，加粗电源线和地线，合理布局电源接触孔，加强去耦，减小相互串扰，提高电路抗辐射能力。

## 2 读出电路测试结果

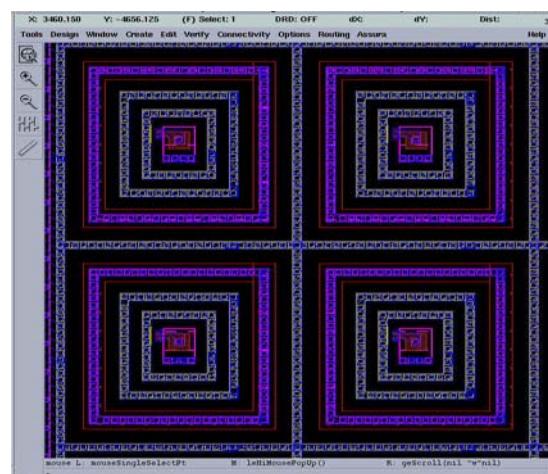

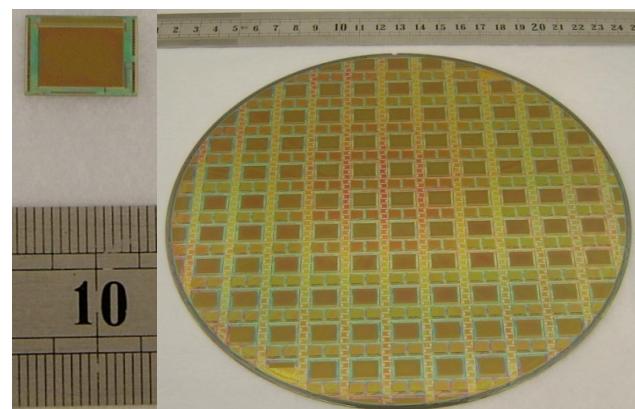

设计好的辐射加固读出电路已流片，流片后的读出电路芯片如图 6 所示。

流片后的读出电路进行电路性能及抗辐射能力测试，低温条件下电路性能测试结果如表 1 所示。

图 5 对 CMOS 管加保护环

Fig.5 Guard banding around NMOS and PMOS transistors

表 1 320×256 读出电路性能测试结果

Table 1 The performance test results of 320×256 ROIC

| 规 格      | 辐 射 前                | 辐 射 后               |

|----------|----------------------|---------------------|

|          | 320×256              |                     |

| 中心距      | 30 μm                |                     |

| 线性输出动态范围 | 2.2 V                | 2.4 V               |

| 最大电荷处理能力 | 1.37 Me <sup>-</sup> | 1.5 Me <sup>-</sup> |

| 最大读出速率   | 4 MHz                | 4 MHz               |

| 帧 频      | ≥100 Hz              | ≥100 Hz             |

| 功 耗      | ≤60 mW               | ≤70 mW              |

从测试结果可以看出，采取加固措施后，电路性能没有受到太大影响。

经读出电路辐射实验测试，本文设计的读出电路抗辐射能力可以达到：抗总剂量：500 rad (Si)，抗剂量率： $1.0 \times 10^9$  rad (Si) / s，并具有一定抗中子辐射能力。抗辐射能力达到设计指标。而未经辐射加固的 CMOS 电路，其抗总剂量抗辐射能力一般

图 6 320×256 抗辐射加固读出电路芯片

Fig.6 The chip of 320×256 radiation hardened ROIC

只能达到 10~50 rad (Si)<sup>[6]</sup>。所以本文采取的加固措施是有效可行的。

## 3 结论

本文设计的电路经过流片、测试，可以看出采取辐射加固措施后，电路性能没有受到影响，且抗辐射能力达到预期设计指标，结果证明本文采用的抗辐射加固方法是切实可行的。目前本文设计的读出电路已经与探测器成功配套并投入生产使用。

### 参考文献：

- [1] Dong PAN, Harry. W. LI, Bogdan. M. WILAMOWSKI. A Radiation-hard Phase-Locked Loop[C]//Proceedings of IEEE, International Symposium on Industrial Electronics, 2003, 2: 901-906.

(下转第 716 页)

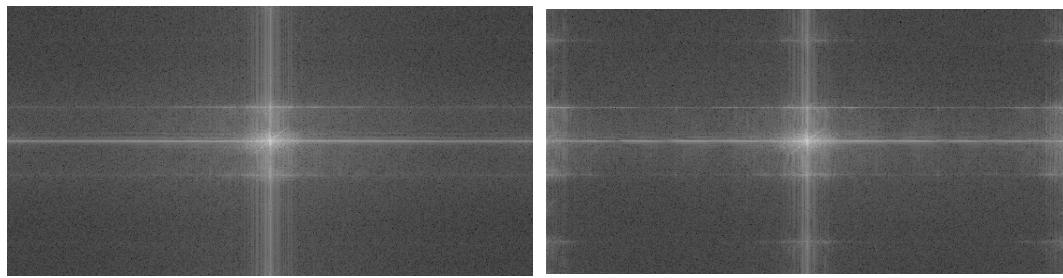

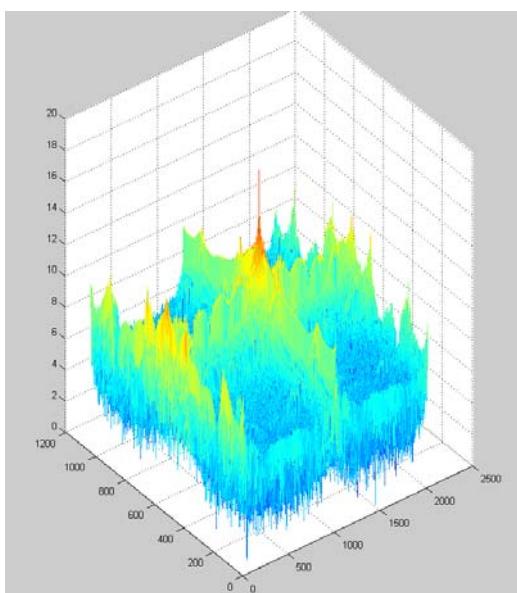

(a) 原始图 (b)The original image

(b)插值重建图 (b) Image after interpolating reconstruction

图 20 图像的 FFT 变换

(a)原始图 (a) The original image

(b)插值重建图 (b) Image after interpolating reconstruction

图 21 图像频谱图 Fig.21

### 3 结束语

我们用中波红外亚像元探测器为对象，开发了一套空间中波红外线列过采样探测系统。该系统能完成图像的采集、传输、实时显示和存储，为分析空间过采样探测提供了一个平台，并为下一步的研究工作打下了基础。

### 参考文献：

- [1] 周峰, 王世涛, 王怀义. 关于亚像元成像技术几个问题的探讨[J]. 航天返回与遥感, 2002, 23(4): 26-33.

- [2] 许元男, 赵远, 斯辰飞, 等. 一种成像型星载激光告警系统的设计[J]. 红外与激光工程, 2006, 35(增刊): 357-360.

- [3] 张才根. 自动检测运动物体的红外探测系统[J]. 应用光学, 2000(S1): 29-32.

- [4] 周世椿. 高级红外光电工程导论[M]. 中科院上海技术物理研究所, 2010.

- [5] 吴诚, 苏君红, 潘顺臣, 等. 对中波与长波红外焦平面热成像的一些探讨[J]. 红外技术, 2002, 24(2): 6-8.

- [6] 赖雪峰, 潘鸣, 裴云天. 中波红外焦平面凝视电路系统的设计与实现[J]. 红外技术, 2005, 27(3): 202-206.

- 学与计算机, 2003(增刊): 68-70.

- [5] E. Mikkola, B. Vermeire, H. J. Barnaby, et al. SET Tolerant CMOS Comparator[C]//Proceedings of IEEE, IEEE Transactions on Nuclear Science, 2004, 51(6): 3609-3614

- [6] 陈桂梅, 许仲德, 苏秀娣. IC 抗辐射加固的方法[J]. 微处理机, 1998 (4): 18-19

(上接第 708 页)

- [2] 姜立娟, 许仲德. CMOS 集成电路抗单粒子加固技术[C]//第九届全国抗辐射电子学与电磁脉冲学术年会论文集, 2007: 194-197.

- [3] 江军, 雷昕, 赵璐, 等. 一种抗辐射加固隔离反馈发生器的研制[C]//第十届全国抗辐射电子学与电磁脉冲学术年会论文集, 2009: 35-40.

- [4] 张小平, 雷天民, 样松, 等. CMOS 集成电路的抗辐射设计[J]. 微电子