# InSb 阳极氧化膜界面特性研究

余黎静, 李延东, 信思树, 郭雨航, 杨文运

(昆明物理研究所, 云南 昆明 650223)

**摘要:** 用阳极氧化的方法在 InSb 衬底上生长氧化膜, 并在阳极氧化膜上镀 Cr/Au 电极以制备 MOS 器件, 通过分析 77 K 时 MOS 器件  $C-V$  特性, 得出 InSb-阳极氧化膜界面的掺杂浓度、界面态密度, 氧化层中的固定电荷密度可动电荷密度等重要参数, 分析其界面特性和制备工艺的关系, 为 InSb 表面的钝化工艺提供参考。

**关键词:** 阳极氧化; MIS 器件;  $C-V$  特性; 界面态密度

中图分类号: TN213 文献标识码: A 文章编号: 1001-8891(2011)04-0191-05

## Interface Properties of Anodized InSb

YU Li-jing, LI Yan-dong, XIN Si-shu, GUO Yu-hang, YANG Wen-yun

(Kunming Institute of Physics, Kunming 650223, China)

**Abstract:** Anodic oxide has been grown on InSb substrate, then the MOS device was fabricated after a layer of Cr/Au gate electrode was evaporated on the oxide. By measuring the capacitance-voltage characteristic at 77K, The electrical properties of the interface, such as impurity concentration, interface state density, fixed charges density mobile ions density has been studied. The conclusions indicate that the properties of the MOS structures are strongly affected by the fabrication procedures, which can provide reference for surface passivation technology.

**Key words:** anodic oxide, MIS device,  $C-V$  characteristic, interface state density

## 引言

InSb 是一种重要的中波红外探测器材料, 它对外界氛围(如各种离子)极为敏感, 容易吸附分子, 原子和离子而产生表面势垒, 影响欧姆接触, 严重时甚至会由于离子导电造成表面漏电<sup>[1]</sup>。因此, 对 InSb 表面进行钝化处理, 对于提高器件的稳定性, 改善器件性能是很有必要的。阳极氧化法由于其制备工艺简单、氧化膜电绝缘性好、漏电少等优点而被广泛用于器件的钝化工艺。

前人对 InSb 的阳极氧化工艺做了大量的研究工作, 特别是针对 InSb 阳极氧化膜的电学特性、界面特性的研究尤为集中<sup>[2-4]</sup>。但是由于 InSb 器件涉及军用, 我们从文献中查到的对具体工艺有用的资料并不多, 很多文献中提及的试验条件和参数, 在我们的试验条件下不一定能取得成功。所以结合我们目前的试验条件, 系统地研究 InSb 阳极氧化膜界面特性, 对于实际的工作有重要的指导意义。

对 MOS 结构  $C-V$  特性的分析是研究半导体表面状态的重要手段<sup>[5]</sup>。通过对 MOS 器件  $C-V$  特性的测试可以系统地研究半导体材料的性能, 及其表面和界面的状况, 表面上生长的绝缘层性质等重要信息。半导体表面态密度、界面陷阱密度等是表征半导体界面特性的重要参量, 本文通过对 MOS 结构空间电荷区  $C-V$  特性的理论分析, 研究了不同的制备工艺下界面的电学特性, 为实际生产中的 InSb 器件钝化工艺提供参考和指导。

## 1 样品的制备

实验中的材料是昆明物理研究所用提拉法制得的 n 型材料, 77 K 时载流子浓度为  $5.1 \times 10^{14} \text{ cm}^{-3}$ 。样品 1 和样品 2 为从同一片 n 型 InSb 衬底上划下来的小片。

阳极氧化时, 把 InSb 晶片的表面连接在正电极(阳极)上, 同负电极(阴极)一起沉浸在电解液中。当在两极加恒定的电压时, 电解液中的  $\text{OH}^-$  离子向阳

极聚集，并在样品表面发生反应生成一层氧化膜，在本实验中，我们用的阳极氧化液是0.1N的KOH溶液。

试验是在室温下时进行，在两个电极间加恒压，观察InSb表面颜色的变化，当电流恒定不变，整个表面都变成均匀的宝蓝色时，关闭电源，取出InSb晶片，并用去离子水冲洗。本实验中，样品1所加的恒压为27V，样品2所加恒压为25V。

对经过阳极氧化的InSb晶片进行光刻、电极膜制备和引线的焊接。为保证和半导体是欧姆接触，而且不损坏绝缘层，在引线焊接时，我们用导电银浆引出金丝。最后得到的MIS器件栅电极尺寸为0.6mm×0.8mm。

## 2 实验结果与分析

### 2.1 表面掺杂浓度

当加到MOS器件上的偏压 $V_G$ 足够大时器件出现强反型，高频扫描时，反型层电荷对MOS器件电容没有贡献，最大电容 $C_{\max}$ 即为 $C_0$ ，最小电容 $C_{\min}$ 和最大电容 $C_{\max}$ 之间有如下关系图<sup>[6]</sup>：

$$\frac{C_{\min}}{C_{\max}} = \frac{1}{1 + \frac{\epsilon_{\text{r}_0}}{\epsilon_{\text{r}_s} d_0} \left( \frac{4\epsilon_0 \epsilon_{\text{r}_s} kT}{q^2 N} \ln \frac{N}{n_i} \right)^{\frac{1}{2}}} \quad (1)$$

式中： $\epsilon_{\text{r}_s}$ 是半导体的相对介电常数； $\epsilon_{\text{r}_0}$ 是氧化层的相对介电常数； $\epsilon_0$ 是真空介电常数； $d_0$ 是氧化层厚度； $C_0$ 为氧化层的单位面积电容。氧化层的相对介电常数取为12。利用式(1)就可以测定InSb表面层中的确实浓度 $N$ 。

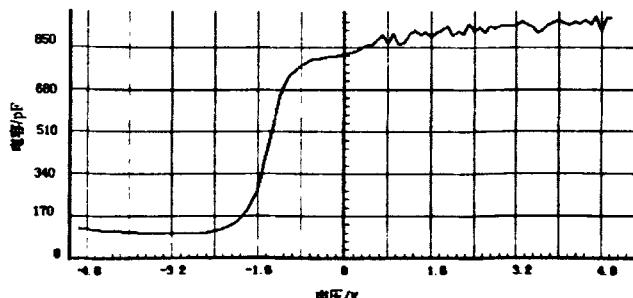

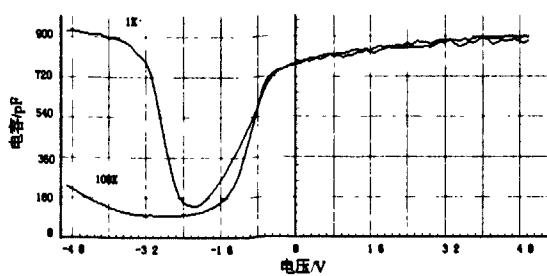

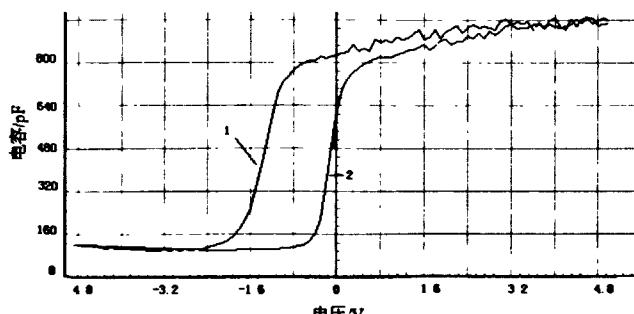

测试均在100kHz的高频下进行，样品1和样品2的高频曲线如图1所示。

通过计算得出，样品1的InSb表面层中的浓度为 $7.4 \times 10^{14} \text{ cm}^{-2}$ ，样品2表面层中的浓度为 $7.2 \times 10^{14} \text{ cm}^{-2}$ ，都比体内的浓度大。这主要是由于在器件制备工艺中引入了一些新的离子，比如工艺过程中会引入

一些污染（比如 $\text{Na}^+$ 等），在阳极氧化过程中会引入了大量的 $\text{K}^+$ 。

通过实际测试的 $C-V$ 曲线和理想曲线的对比还可以得出下面的结论：样品1的 $C-V$ 曲线的平带电压为-1.42V，说明是受正电荷的影响向负方向移动，由此判断表面的电荷为正电荷，由偏移距离还可以计算出表面的固定电荷密度为 $1.9 \times 10^{12} \text{ cm}^{-2}$ ；样品2的 $C-V$ 曲线的平带电压为-0.87V，表面电荷也为正，由偏移距离计算出表面的固定电荷密度为 $1.01 \times 10^{12} \text{ cm}^{-2}$ 。这与Hong Zhang在文献[4]中的结论不符，在文献中，InSb表面经过阳极氧化工艺后，表面电荷为负电荷。我们曾对在InSb衬底上用和样品2相同工艺生长的阳极氧化层表面做过扫描电镜分析，发现氧化层中除了含有In原子、Sb原子和O原子外，还含有大量的带正电的K离子。这与我们试验中的结果一致。

通过 $C-V$ 曲线还可以很快地计算出样品氧化层的厚度：样品1中氧化层厚度为516Å，样品2中的氧化层厚度为570Å。这时因为在一定的范围内，所加偏压越大，氧化速度就越快，表面的原子层很快被氧化，就会阻挡下面的原子层被氧化，样品1所加偏压更大，它的氧化层就比2的薄。我们在阳极氧化的过程中，在适当的范围内，尽量用小的偏压来进行氧化，以增加氧化层的厚度，提高其耐击穿性。

### 2.2 表面态密度

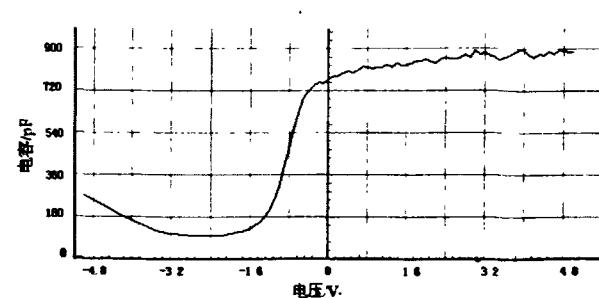

当加到MOS器件上的偏压 $V_G$ 改变时，表面势 $V_s$ 也随之改变，费米能级在禁带中的位置也发生改变，界面态的填充几率就要发生变化，表面态电荷 $Q_{ss}$ 随之发生变化，即发生充放电，相当于表面有一个电容 $C_{ss}$ ，这时MOS器件的电容除了InSb衬底的电容 $C_{sc}$ 外，还有表面态电容 $C_{ss}$ 。但是当加在MOS器件上的信号是高频信号时，表面态来不及发生充放电，这时高频信号对界面的电容没贡献。这时的等效电路如图2所示。

(a) 样品 1

(b) 样品 2

图1 100K时 $C-V$ 曲线

Fig.1  $C-V$  curve at 100K

图2 等效电路

Fig.2 equivalent circuit

由准静态  $C-V$  法可得表面态密度为<sup>[7]</sup>:

$$N_{ss} = dQ_{ss}/(qdV_s) = C_{ss}/q \quad (2)$$

由半导体的能带理论,

$$E_c - E_s = \frac{1}{2}E_b + (E_i - E_F) \pm q|\psi_s| \quad (3)$$

式中:  $\psi_s$  为表面势;  $E_s$  为表面能级。

联立(2)、(3)可以得到表面态密度和能量分布的关系。

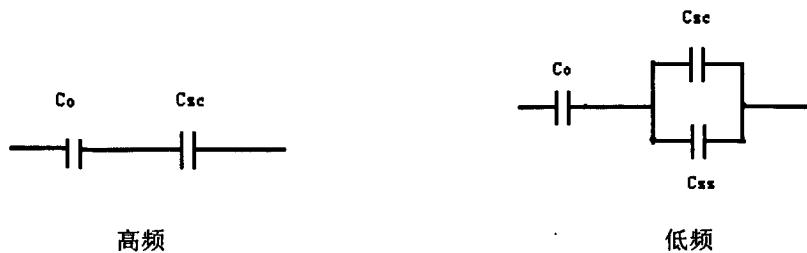

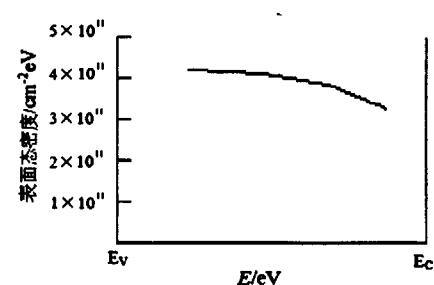

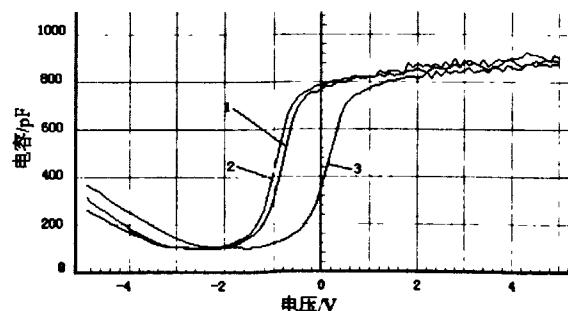

由图 3(b)可以看出样品 1 表面态在禁带中的分布情况, 在整个禁带中, 界面态密度分布比较均匀, 在  $4 \times 10^{15} \text{ cm}^{-2} \text{ eV}$ 。

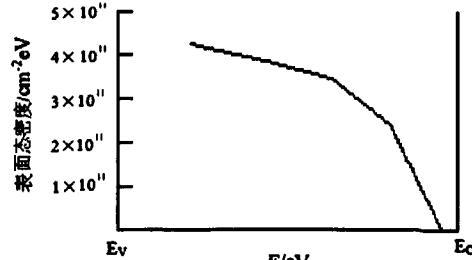

由图 4(b)可以看出样品 2 表面态在禁带中的分布情况, 在靠近导带底时, 表面态密度最低。

和 Hong Zhang 在文献<sup>[4]</sup>中的报道的结果 (界面态密度为  $2.3 \times 10^{11} \text{ cm}^{-2} \text{ eV}$ ) 相比较, 样品 1 的界面态密度偏大, 样品 2 界面态密度比较接近。这很可能是由于 InSb 衬底晶格缺陷、损伤和界面处杂质引入界面态所导致。为了减小界面态的影响, 可以尝试用退

火的方法处理样品以降低界面态密度<sup>[6]</sup>。

### 2.3 氧化层电荷

MOS 结构氧化层中的电荷包括可动电荷、固定电荷和陷阱电荷。用正、负偏压温度处理的方法 (简称土 BT 处理) 可以将可动电荷  $Q_f$  和固定电荷  $Q_{fc}$  区分开来。

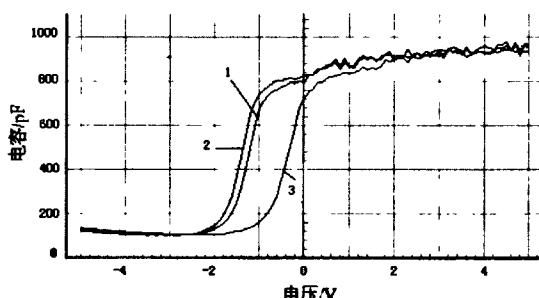

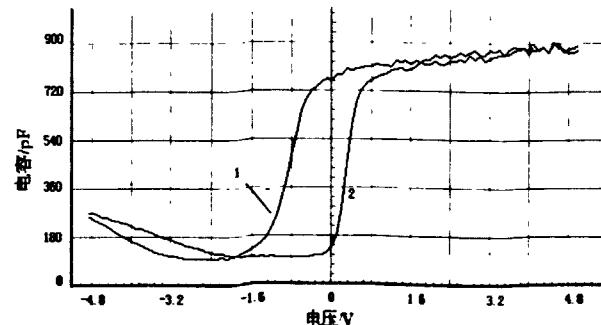

在做土 BT 处理时, 我们将器件装在金属杜瓦中, 冷却至液氮温度, 在暗背景下做一次  $C-V$  测试, 记为曲线 1; 然后将器件回对室温, 在器件两端加  $-1.5 \text{ V}$  的偏压 (金属电极接负, InSb 衬底接正), 10 min 后, 在维持偏压和暗背景的条件下, 重新把器件冷却到液氮温度, 撤去偏压, 再进行一次  $C-V$  测试, 记为曲线 2, 这就完成了一个负 BT 试验。在进行正 BT 试验时, 给样品加  $1.5 \text{ V}$  的正偏压 (即金属电极接正, InSb 衬底接负), 其它条件相同, 再进行  $C-V$  测试, 记为曲线 3。

(a)  $C-V$  特性曲线 (样品 1)

图3  $C-V$  特性曲线及表面态密度分布 (样品 1)

Fig.3  $C-V$  curve and interface state density distribution (sample 1)

(b) 表面态密度分布 (样品 1)

(a)  $C-V$  特性曲线 (样品 2)

图4  $C-V$  特性曲线及表面态密度分布 (样品 2)

(b) 表面态密度分布 (样品 2)

Fig.4  $C-V$  curve and interface state density distribution (sample 2)

经过土BT处理后, 氧化层中的固定电荷  $Q_{fc}$  和可动电荷  $Q_l$  可由(4)式和(5)式求出<sup>[5]</sup>:

$$Q_{fc} = -\frac{C_o(V_{ms} + V_{FB2})}{q} \quad (4)$$

$$Q_l = \frac{C_o \Delta V_{FB}}{q} \quad (5)$$

式中:  $V_{ms}$  为由于金属半导体功函数的不同而引起的  $C-V$  曲线的偏移量,  $V_{FB2}$  为负 BT 处理后  $C-V$  曲线(曲线 2) 的偏移量,  $\Delta V_{FB}$  是负 BT 处理(曲线 2) 和正 BT 处理(曲线 3) 时  $C-V$  曲线的偏移量之差。

由样品 1 的土 BT 处理前后的  $C-V$  特性曲线, 可求出  $\Delta V_{FB}$  和  $V_{FB2}$ 。由此可以计算出样品 1 可动电荷  $Q_l$  和固定电荷  $Q_{fc}$ :

固定电荷面密度:

$$Q_{fc} = -\frac{C_o(V_{ms} + V_{FB2})}{q} = 1.7 \times 10^{12} \text{ cm}^{-2}$$

可动电荷面密度:

$$Q_l = \frac{C_o \Delta V_{FB}}{q} = 2.3 \times 10^{12} \text{ cm}^{-2}$$

由样品 2 的土 BT 处理前后的  $C-V$  特性曲线, 可求出  $\Delta V_{FB}$  和  $V_{FB2}$ 。求得样品 2 的可动电荷  $Q_l$  和固定电荷  $Q_{fc}$ :

固定电荷面密度:

$$Q_{fc} = -\frac{C_o(V_{ms} + V_{FB2})}{q} = 1 \times 10^{12} \text{ cm}^{-2}$$

图 5 BT 处理前后  $C-V$  特性曲线(样品 1)

Fig.5  $C-V$  curve before and after the BT process(sample 1)

图 7 滞后回线(样品 1)

Fig.7 Hysteresis effect (sample 1)

可动电荷面密度:

$$Q_l = \frac{C_o \Delta V_{FB}}{q} = 1.9 \times 10^{12} \text{ cm}^{-2}$$

样品 2 的固定电荷密度和可动电荷密度都比样品 1 低。由此可以看出两种工艺的优劣性, 在相对小的偏压下生长的阳极氧化膜更利于器件的性能和稳定性。

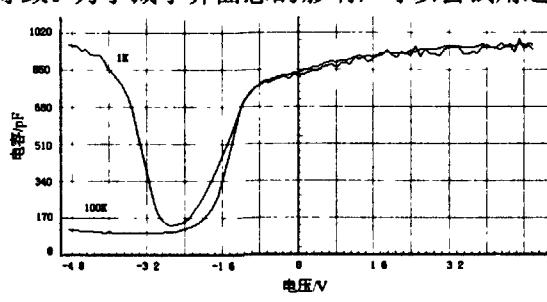

在  $C-V$  测试中我们发现与测试有关的滞后回线, 如图 7 和图 8 所示。

我们测试电容时, 先从负电压扫到正电压(曲线 1), 然后从正电压扫到负电压(曲线 2)。从正到负和从负到正所测得的  $C-V$  曲线有一个偏移。

这个现象是由于陷阱电荷引起的。董硕等<sup>[8]</sup>用 XPS 对 InSb 表面氧化物含量进行分析, 分析结果表明 Sb 含量远低于其化学当量比。氧化层中 Sb 离子的缺失将会形成正的陷阱。在每一次加正的偏压时, 电子都会从 InSb 衬底进入陷阱中。因此, 实际的  $C-V$  测试中, 当由正向负回扫时曲线都会向右平移一定的距离。

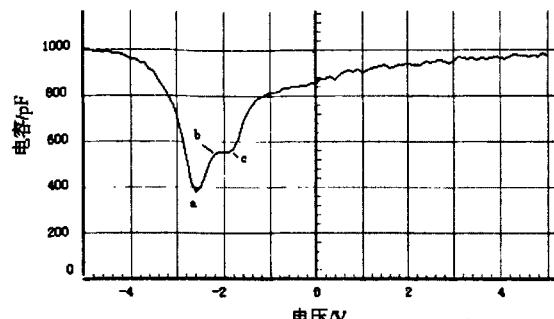

#### 2.4 $C-V$ 曲线的畸变

在测试的过程中, 会发现一些  $C-V$  曲线出现台阶状的畸变现象。如图 9 所示。

图 6 BT 处理前后  $C-V$  特性曲线(样品 2)

Fig.6  $C-V$  curve before and after the BT process(sample 2)

图 8 滞后回线(样品 2)

Fig.8 Hysteresis effect (sample 2)

图 9  $C-V$  曲线的畸变

Fig.9 aberration of  $C-V$  curve

分析其产生的原因,一般也是由氧化层部分区域低击穿产生漏电引起的<sup>[9]</sup>,如图9的曲线所示,氧化层在ab段几乎没有漏电,曲线形状和趋势都正常;到bc段时出现漏电,从而导致 $C/C_0$ 的值减小。于是 $C-V$ 曲线就出现了台阶,发生畸变。由于MOS器件漏电的程度不同,具体机制也不同,从而导出现畸变 $C-V$ 曲线的形状各异。但不管漏电的情况怎样,这些异常的特性都通过 $C-V$ 曲线的异常反应出来了。所以 $C-V$ 测试也可以作为检测漏电的一个方法。

### 3 结论

在半导体器件的生产和研制中,表面钝化对提高器件的性能和稳定性有至关重要的作用,阳极氧化法由于其一系列的优点而被广泛应用于器件的钝化工艺。 $C-V$ 测试是极为重要的研究半导体表面性能的手段。本文用对不同的氧化条件进行了研究,求出了样品表面的掺杂浓度,界面态密度和氧化层中各种电荷的分布情况,同时对两种不同的阳极氧化工艺进行了分析评价,指出在一定范围内,小电压条件下制备的氧化膜更有利于器件的性能。论文还分析了测试中

$C-V$ 曲线的台阶畸变现象出现的原因。本文的工作对于研究和评价InSb的阳极氧化有重要的意义,同时也为实际工艺中的表面钝化工艺提供参考和指导。

### 致谢

陈爱萍、郭雨航、袁俊、莫镜辉、信思树、孙祥乐为本文的实验工作提供了不少帮助,在文章的撰写过程中,邓功荣和龚晓霞给予了很多建议和帮助,作者谨致谢意。

### 参考文献:

- [1] 王红妹. InSb 光伏探测器钝化对电学性能的影响[J]. 红外与激光工程, 1982, 11(4): 25-30.

- [2] A. Etchelis, C. W. Fischer. Interface state density and oxide charge measurements on the metal-anodic-oxide-InSb system[J]. *Journal of Applied Physics*, 1976, 47(10): 4605-4610.

- [3] James C. Kim, Member, IEEE. Interface properties of InSb MIS structures[J]. *IEEE transactions on parts, hybrids, and packaging*, 1974, 10(4): 200-207.

- [4] Hong Zhang. Studies of the Metal-Oxide-Semiconductor Structures On InSb[D]. Canada, McGill University, 1996.

- [5] 孙以材. 半导体测试技术[M]. 北京: 冶金工业出版社, 1984.

- [6] 刘恩科, 朱秉升, 罗晋生, 等. 半导体物理学[M]. 北京: 国防工业出版社, 1979.

- [7] 钱敏, 刘蓓, 辛煜. 准静态  $C-V$  法测量硅表面态密度分布及数据处理[J]. 半导体技术, 2007, 32(7): 577-580.

- [8] 董硕, 雷静. InSb 的氧化膜研究[C]//2003 年全国光电技术学术交流会暨第十六届全国红外科学技术交流会论文集, 北京: 中国宇航学会.

- [9] 陈永珍. 集成电路中栅介质膜的  $C-V$  测试误差分析及其修正模型[J]. 半导体技术, 1994, 1(1): 37-45.